**Funktelefon C-Netz**

## **Gerätebeschreibungen**

**Band 1**

**SIEMENS**

**Funktelefon C-Netz LM4**

**Gerätebeschreibungen**

**A42023-H1-X-1-18**

**Band 1**

---

Siemens-Aktiengesellschaft

Herausgegeben vom Bereich Öffentliche Vermittlungssysteme

Hofmannstraße 51, D-8000 München 70

Verfasser: Dr. Schmidt

Weitergabe sowie Vervielfältigung dieser Unterlage, Verwertung und Mitteilung ihres Inhalts nicht gestattet, soweit nicht ausdrücklich zugestanden. Zu widerhandlungen verpflichten zu Schadenersatz. Alle Rechte vorbehalten, insbesondere für den Fall der Patenterteilung oder GM-Eintragung.

Technische Änderungen vorbehalten.

© Siemens AG 1989

A42023-H1-X-1-18

**SIEMENS**

**FDS**

**-H72-B5-**

**SAE

-H76-B1-**

FME

H129-F1-

**PFG**

**-H130-E2-**

**FKM-SPK**

**-H131-E1-**

# Fu Tel C-Netz Gerätebeschreibungen LM 6

## **Band 1**

Herausgegeben vom Bereich Öffentliche Vermittlungssysteme

Hofmannstraße 51, D-8000 München 70

Verfasser: SÖ ETG 22, Wien

Weitergabe sowie Vervielfältigung dieser Unterlage, Verwertung und Mitteilung ihres Inhalts nicht gestattet, soweit nicht ausdrücklich zugestanden. Zu widerhandlungen verpflichten zu Schadensersatz. Alle Rechte vorbehalten, insbesondere für den Fall der Patenterteilung oder GM-Eintragung.

Technische Änderungen vorbehalten.

© Siemens AG 1989

**Funkdatensteuerung (FDS)****S42023-H72-B5, -B6****Inhalt**

|                                                                                                          | Seite |

|----------------------------------------------------------------------------------------------------------|-------|

| 1      Übersicht .....                                                                                   | 5     |

| 1.1     Funkdatensteuerung in der Basisstation .....                                                     | 5     |

| 1.2     Aufgabenstellung .....                                                                           | 9     |

| 1.2.1   Betriebstechnische Aufgaben .....                                                                | 9     |

| 1.2.2   Vermittlungstechnische Aufgaben .....                                                            | 9     |

| 1.2.3   Sicherheitstechnische Aufgaben .....                                                             | 9     |

| 1.2.4   Funktechnische Aufgaben .....                                                                    | 10    |

| 2      Schnittstellen .....                                                                              | 11    |

| 2.1     Externe Schnittstellen .....                                                                     | 11    |

| 2.1.1   Schnittstelle zur Funkperipherie Funkdatensteuerung (FDS)<br>und Prüf-/Bedienrechner (PBR) ..... | 11    |

| 2.1.1.1   Sendeschnittstelle .....                                                                       | 11    |

| 2.1.1.2   Empfangsschnittstelle .....                                                                    | 12    |

| 2.1.2   Schnittstelle zur Signalanpaßeinheit (SAE) .....                                                 | 12    |

| 2.1.3   Takschnittstelle zum Phasenempfänger (PHE) .....                                                 | 14    |

Herausgegeben von Bereich

Öffentliche Vermittlungssysteme

Hofmannstraße 51, D-8000 München 70

|           |                                                     |    |

|-----------|-----------------------------------------------------|----|

| 2.1.4     | Schnittstelle zur Parallel-FDS .....                | 14 |

| 2.1.4.1   | Bidirektionale Leitungen .....                      | 15 |

| 2.1.4.2   | Unidirektionale Leitungen .....                     | 15 |

| 2.1.5     | Sicherheitstechnische Schnittstellen .....          | 16 |

| 2.1.5.1   | Schnittstellen zu den Netzteilen .....              | 16 |

| 2.1.5.2   | Schnittstelle zur FDS2 .....                        | 18 |

| 2.1.5.3   | Schnittstelle Netzteil - Baugruppe Aktivdatei ..... | 18 |

| 2.2       | Interne Schnittstellen .....                        | 19 |

| 2.2.1     | FDS-Bussystem .....                                 | 19 |

| 2.2.1.1   | Adreß- und Datenbus .....                           | 19 |

| 2.2.1.2   | Steuerbus .....                                     | 21 |

| 2.2.2     | Taktschnittstelle .....                             | 22 |

| 2.2.3     | Interrupt-Signale .....                             | 22 |

| 2.2.4     | Sicherheitstechnische Schnittstellen .....          | 25 |

| 3         | Funkdatensteuerung (FDS) .....                      | 26 |

| 3.1       | Datenkonzentrator DKo .....                         | 26 |

| 3.1.1     | DKo-Prozessor S42024-H179-D1 .....                  | 26 |

| 3.1.1.1   | CPU .....                                           | 26 |

| 3.1.1.2   | Interrupt-Steuerung PIC .....                       | 29 |

| 3.1.1.3   | I/O-Adreßdecoder .....                              | 31 |

| 3.1.1.4   | Parallel-I/O-Ports .....                            | 32 |

| 3.1.1.5   | Speicheradreßdecoder .....                          | 33 |

| 3.1.1.6   | Speicher .....                                      | 34 |

| 3.1.2     | DKo-Zeitgeber S42024-H188-C1 .....                  | 35 |

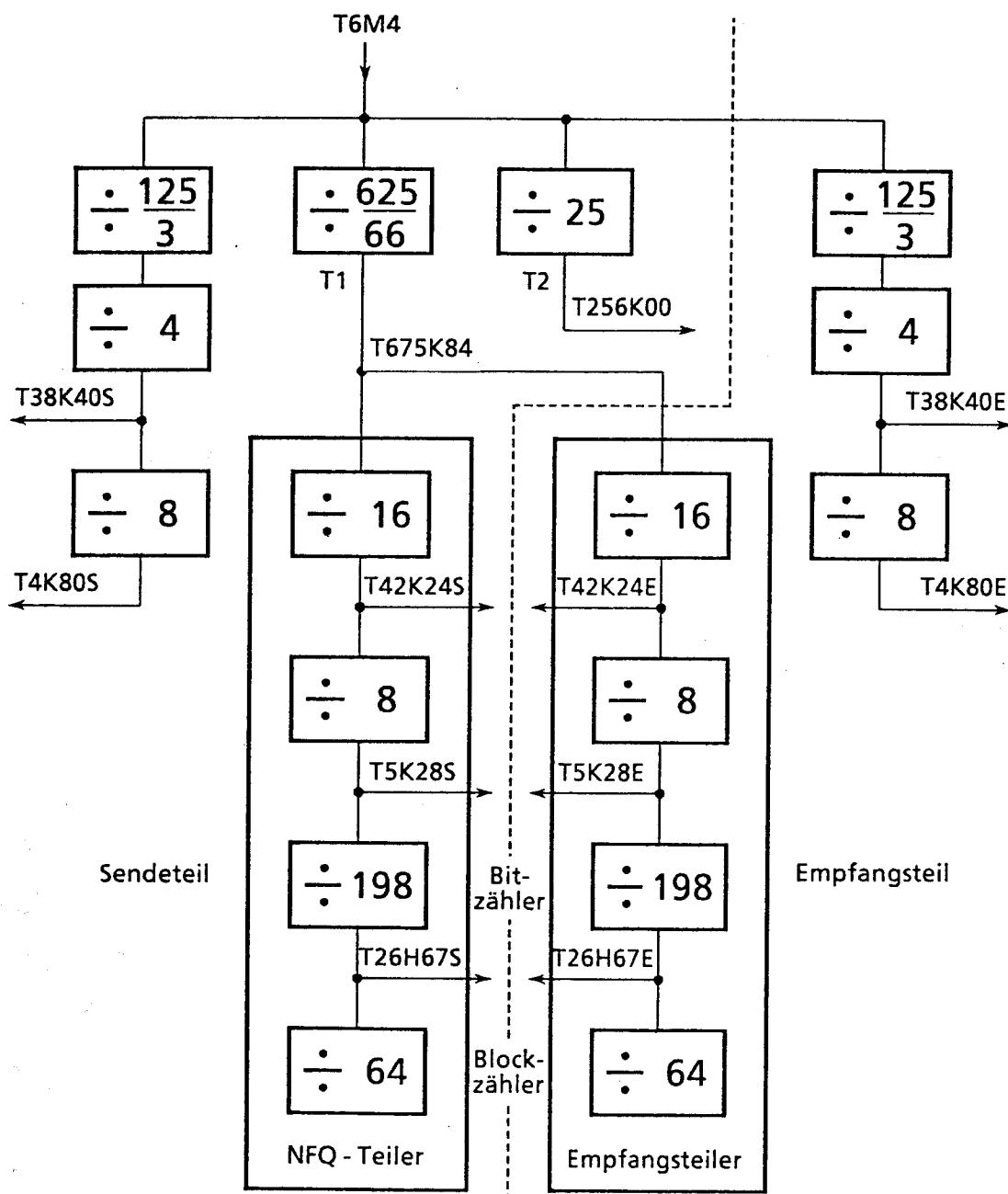

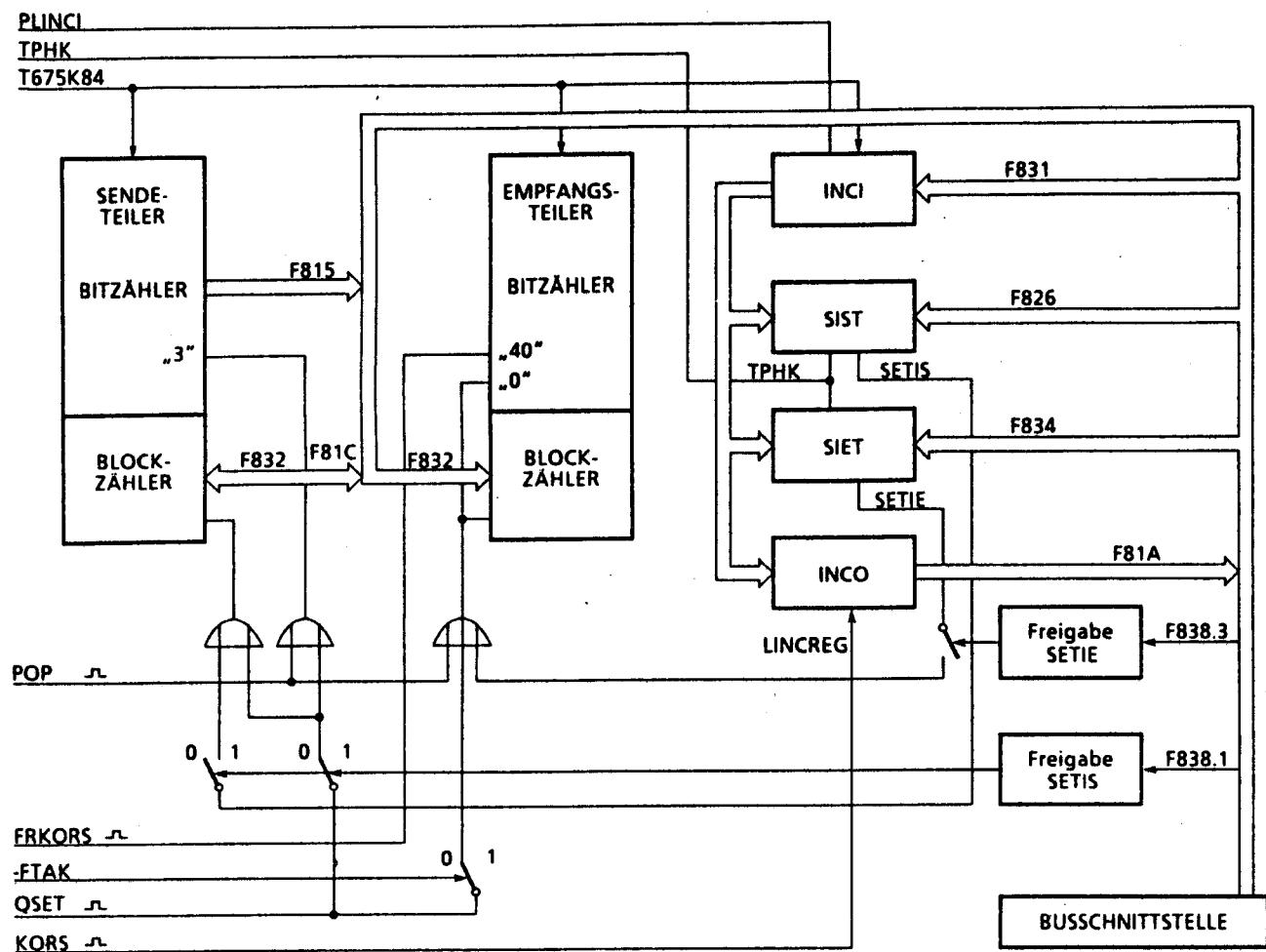

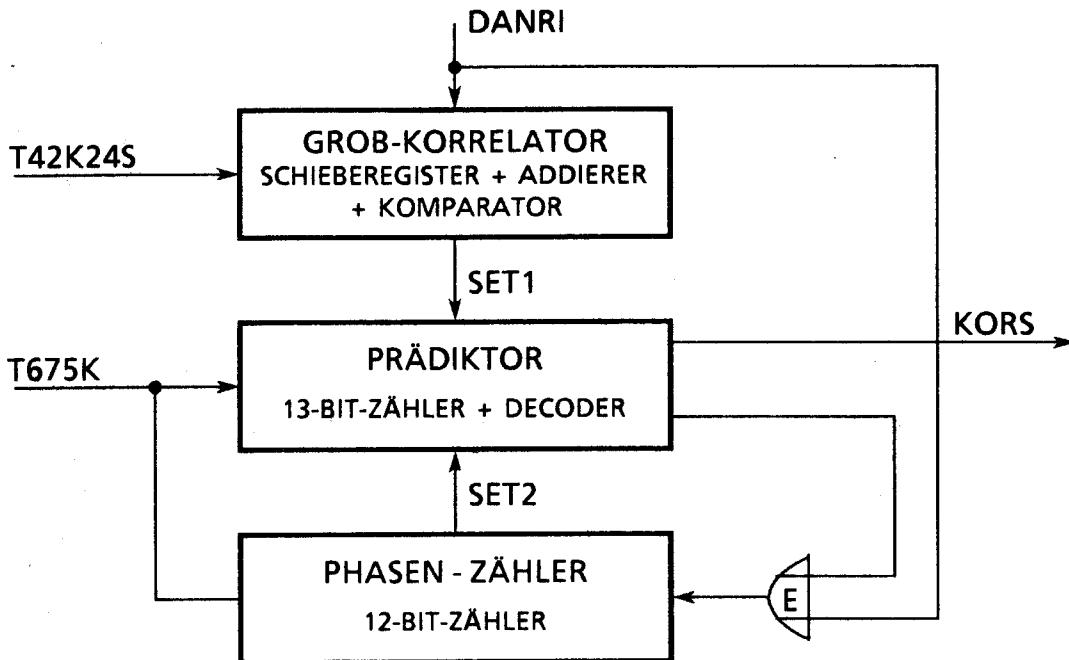

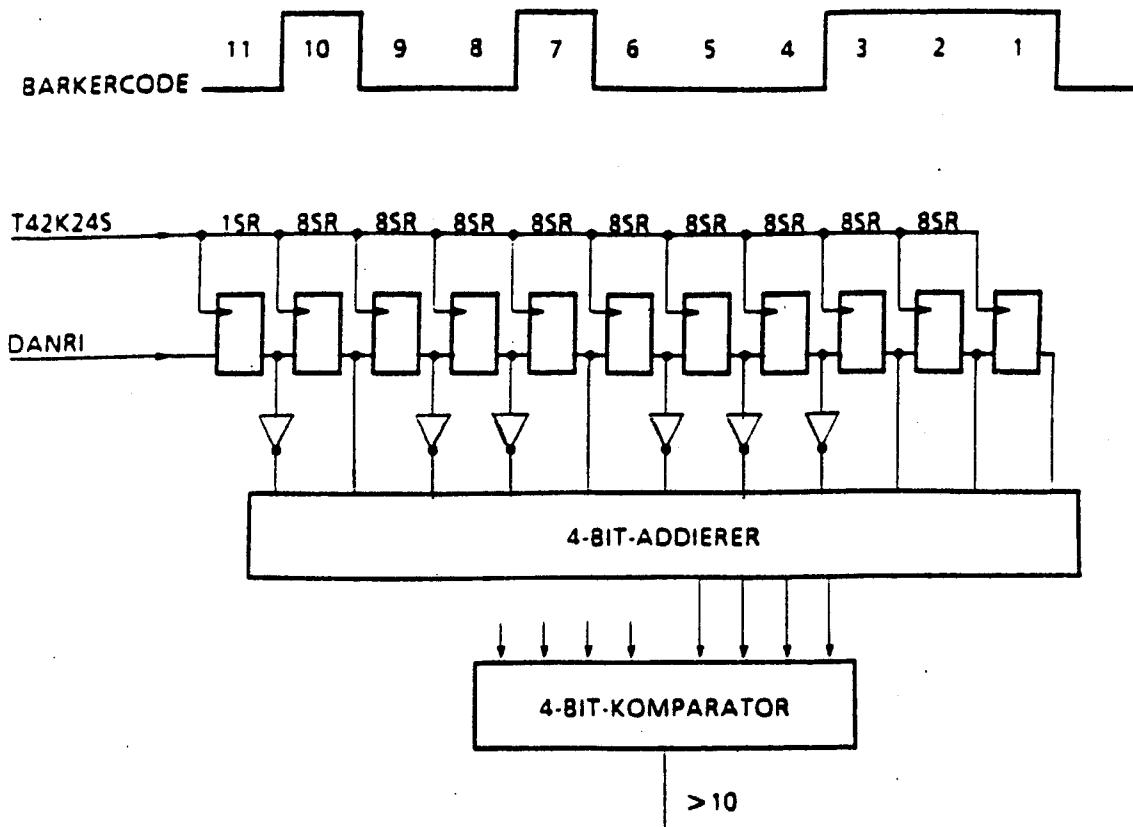

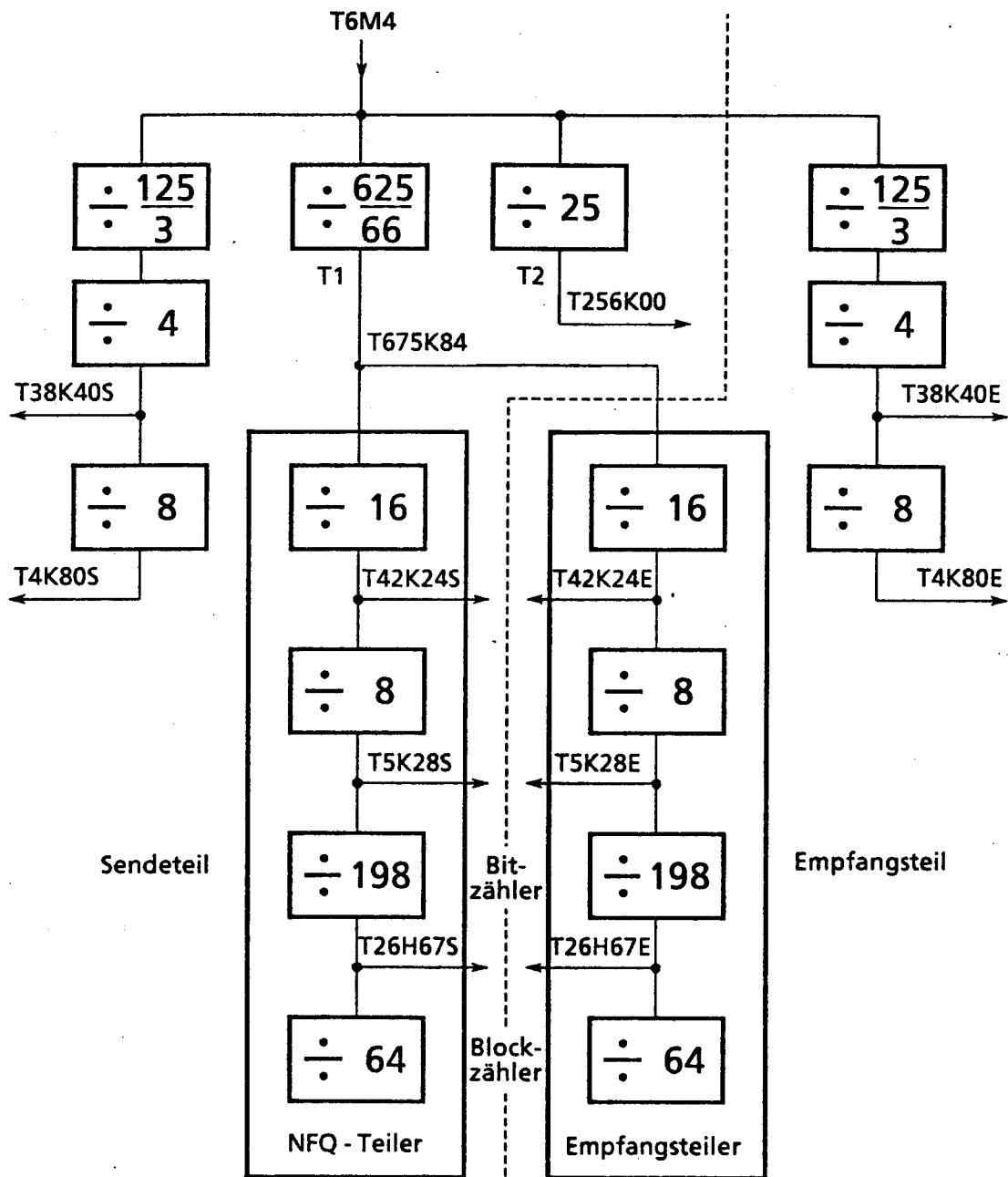

| 3.1.2.1   | Takterzeugung T256K .....                           | 37 |

| 3.1.2.2   | Zeitgeber 0 .....                                   | 39 |

| 3.1.2.2.1 | Takterzeugung INT-T37, 5MS-L .....                  | 39 |

| 3.1.2.2.2 | Blockzähler .....                                   | 39 |

| 3.1.2.2.3 | Überwachungstor .....                               | 39 |

| 3.1.2.3   | Zeitgeber 1, 2 .....                                | 40 |

| 3.1.2.4   | Überwachungstor und Verzögerungslogik .....         | 41 |

| 3.1.2.5   | Adreßdecoder .....                                  | 41 |

| 3.1.2.6   | Serielle Schnittstelle USART 2661 .....             | 41 |

| 3.1.3     | Schnittstelle ZZK S42024-H187-D1 .....              | 42 |

| 3.1.3.1   | Steuerlogik .....                                   | 44 |

| 3.1.3.2   | Seriell-/Parallel-Wandler .....                     | 45 |

| 3.1.3.3   | Kontrollogik .....                                  | 47 |

| 3.1.3.4   | Adreßdecoder .....                                  | 54 |

| 3.1.3.5   | I/O-Ports .....                                     | 54 |

| 3.1.3.6   | Speicher .....                                      | 54 |

| 3.1.3.7   | ZZK-Schleifentest .....                             | 55 |

|           |                                                         |     |

|-----------|---------------------------------------------------------|-----|

| 3.1.4     | Schnittstelle FKS S42024-H186-C1 .....                  | 56  |

| 3.1.4.1   | Empfänger .....                                         | 59  |

| 3.1.4.2   | Multiplexer .....                                       | 62  |

| 3.1.4.3   | Latch .....                                             | 62  |

| 3.1.4.4   | Speicher .....                                          | 62  |

| 3.1.4.5   | Sender .....                                            | 64  |

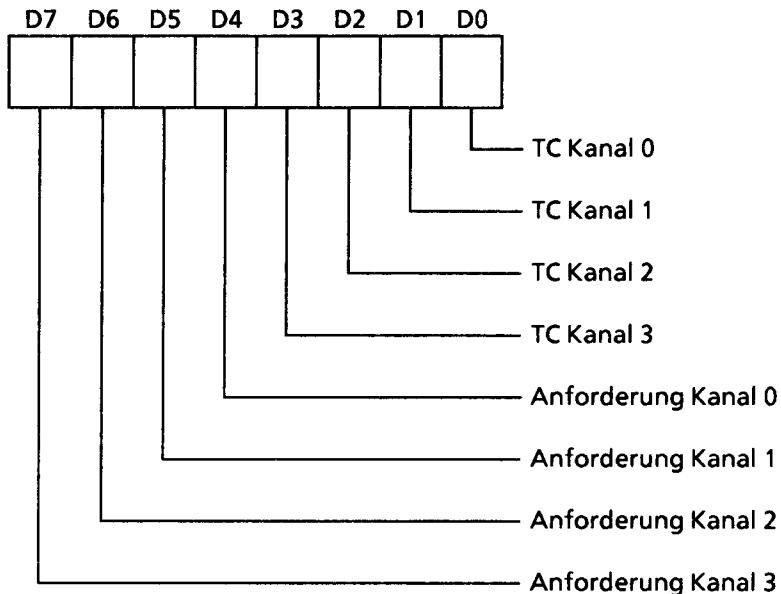

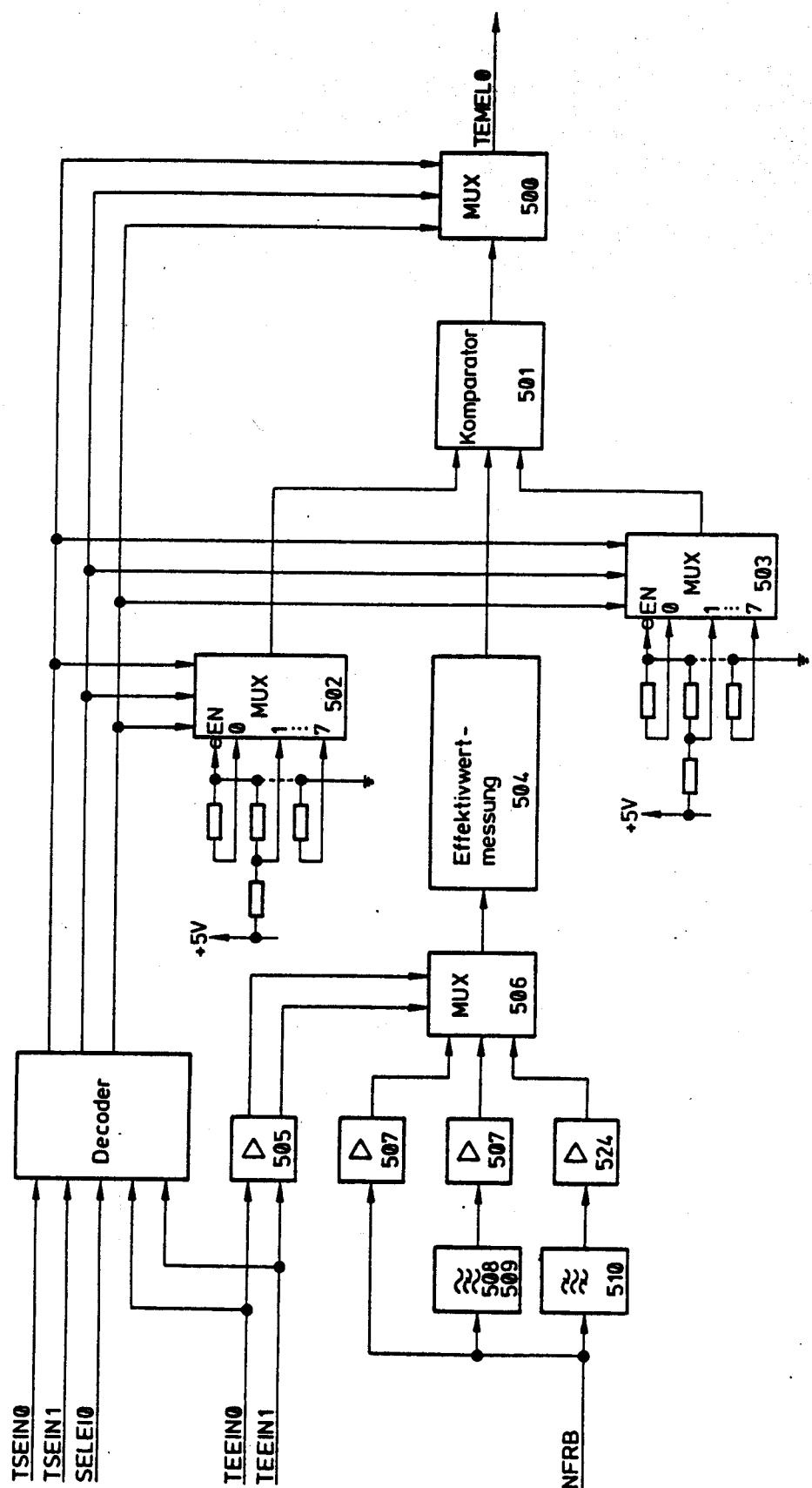

| 3.2       | Dateien- und Kanalverwaltung DKV .....                  | 65  |

| 3.2.1     | DKV-Prozessor S42024-H180-D1 .....                      | 66  |

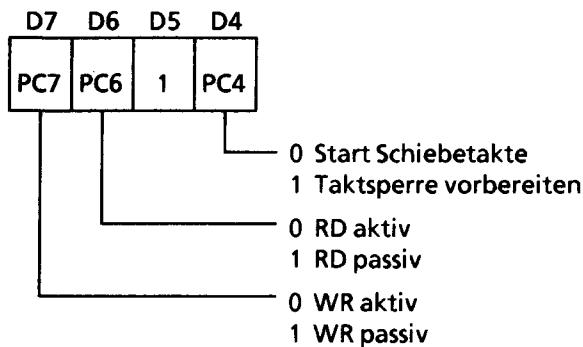

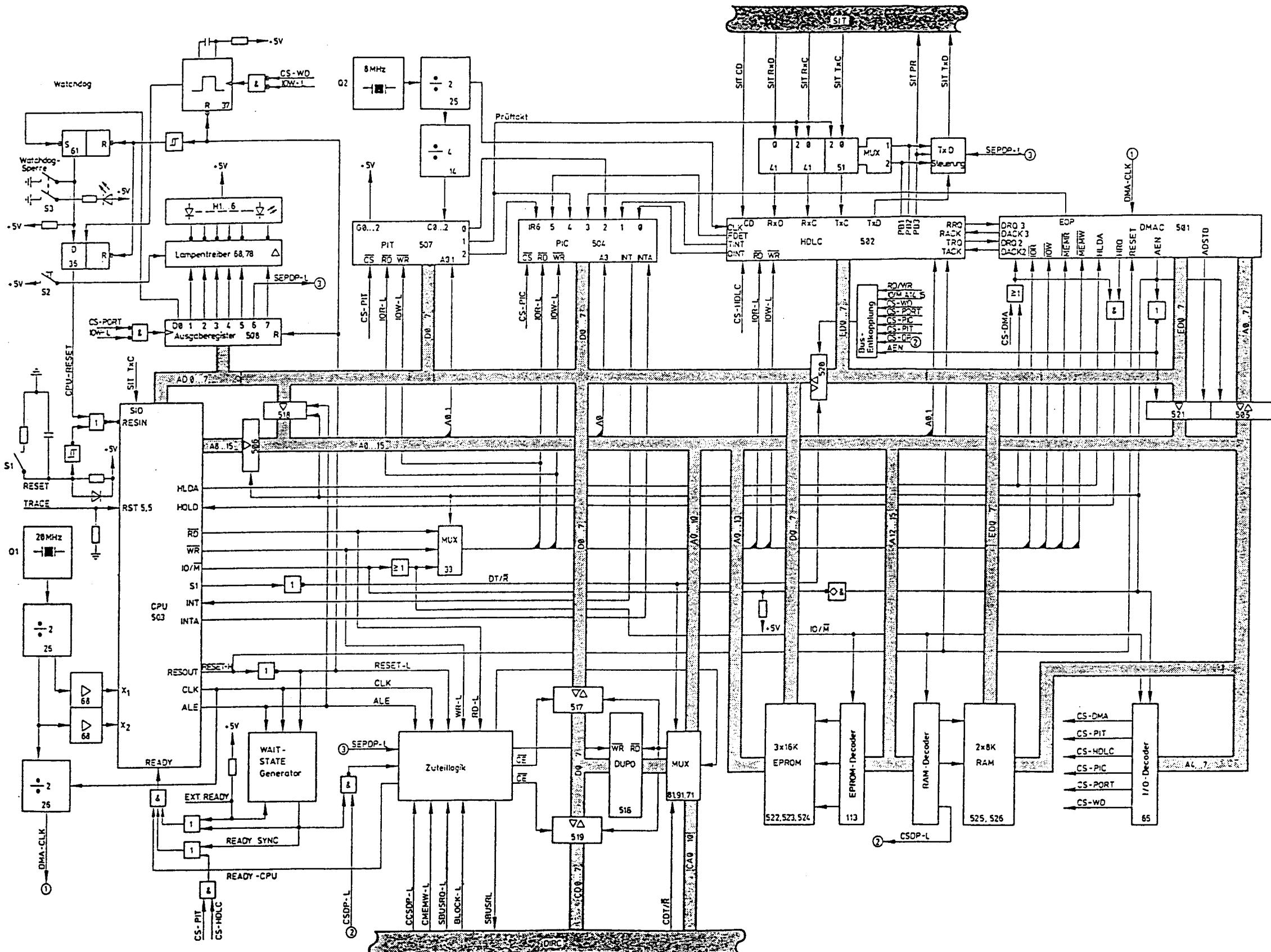

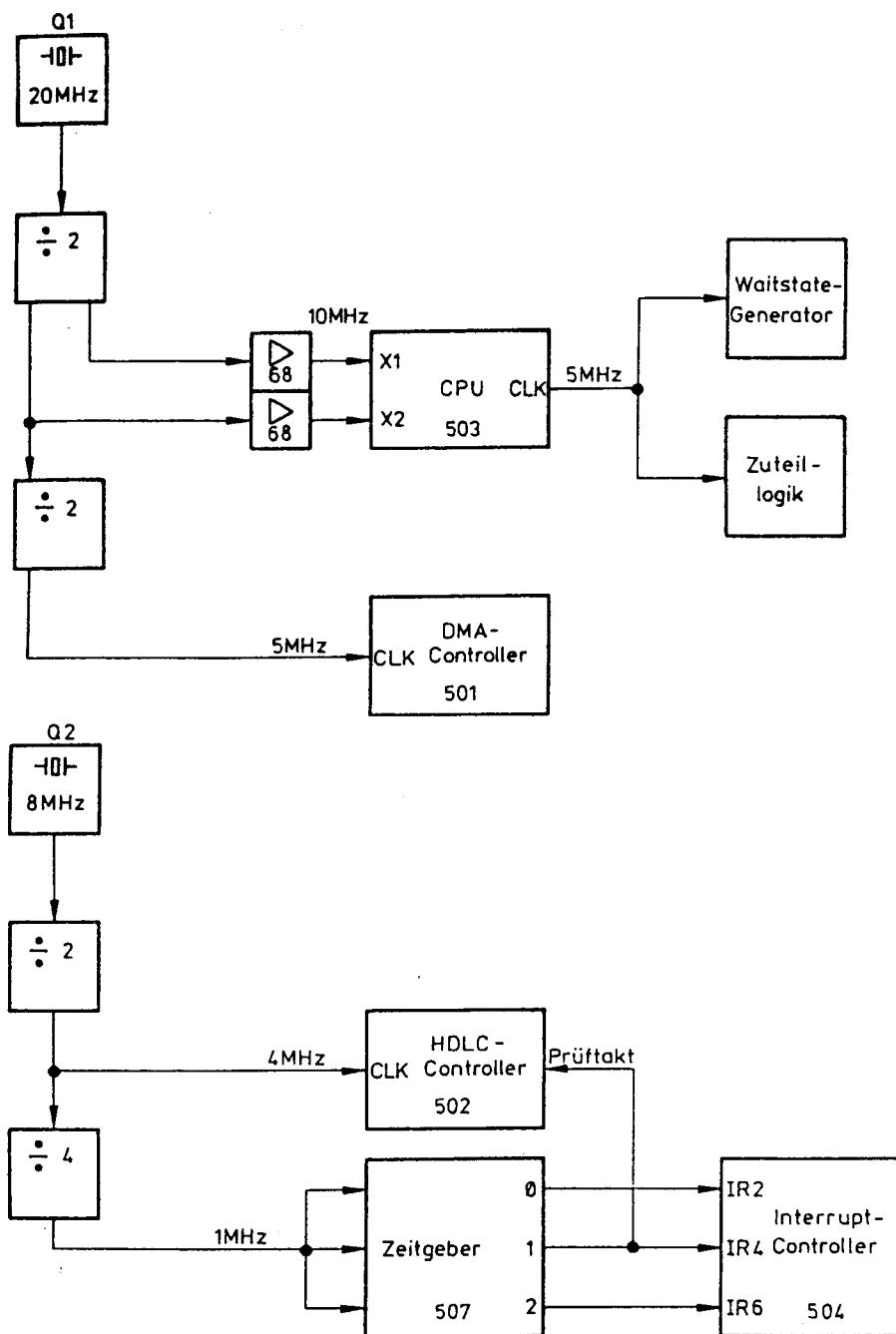

| 3.2.1.1   | CPU mit Taktgenerator .....                             | 69  |

| 3.2.1.2   | DMA-Steuerung .....                                     | 69  |

| 3.2.1.3   | Interrupt-Steuerung PIC .....                           | 75  |

| 3.2.1.4   | Zeitgeber .....                                         | 76  |

| 3.2.1.5   | Parallel-I/O-Baustein PIO .....                         | 78  |

| 3.2.1.5.1 | Port A .....                                            | 78  |

| 3.2.1.5.2 | Port B .....                                            | 79  |

| 3.2.1.5.3 | Port C .....                                            | 80  |

| 3.2.1.6   | DMA- und Bussteuerlogik .....                           | 80  |

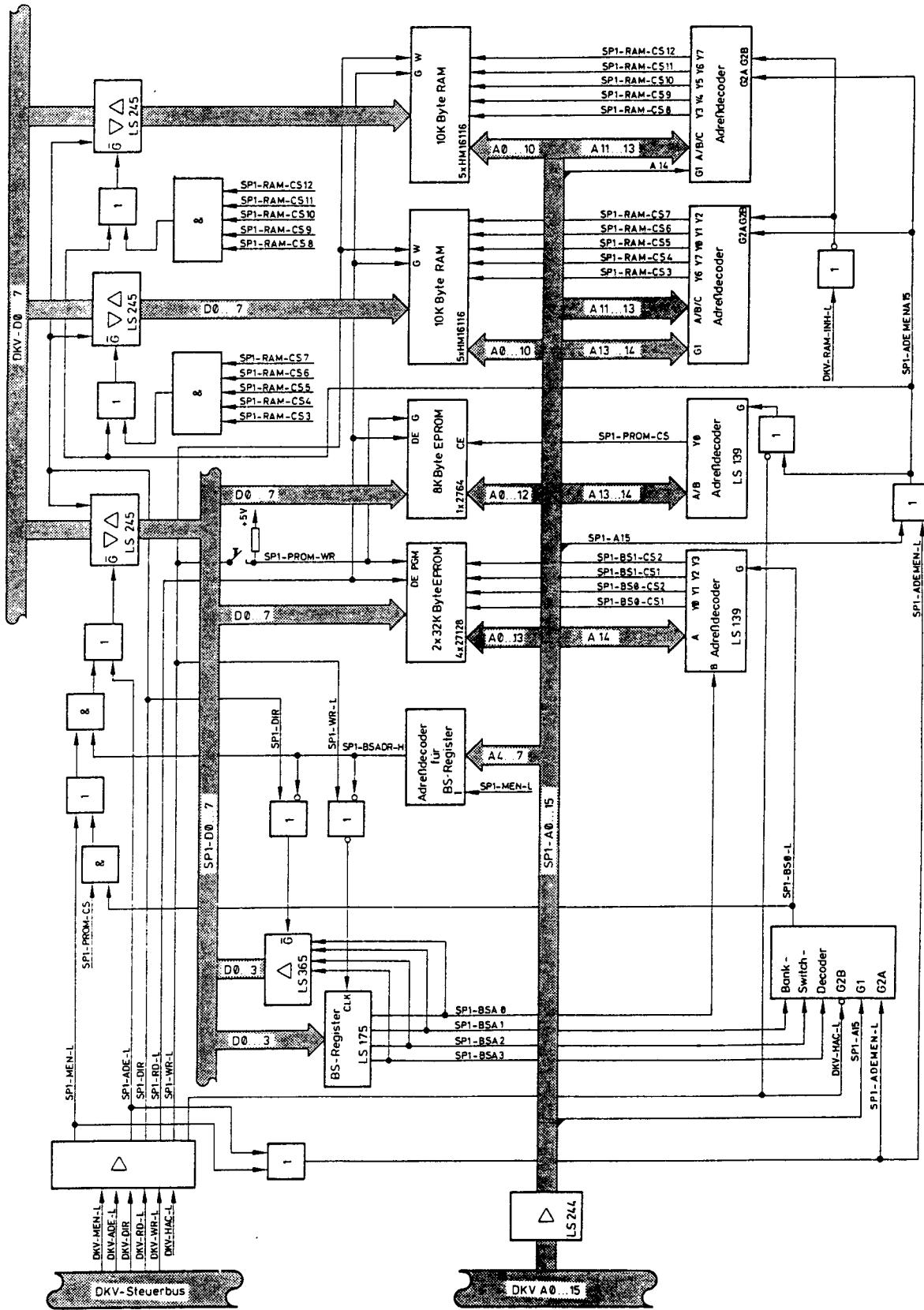

| 3.2.2     | DKV-Speicher 1 S42024-H181-C1 .....                     | 80  |

| 3.2.2.1   | 8-Kbyte EPROM .....                                     | 81  |

| 3.2.2.2   | Speicherbank 0/1 .....                                  | 81  |

| 3.2.2.3   | RAM-Bereich .....                                       | 81  |

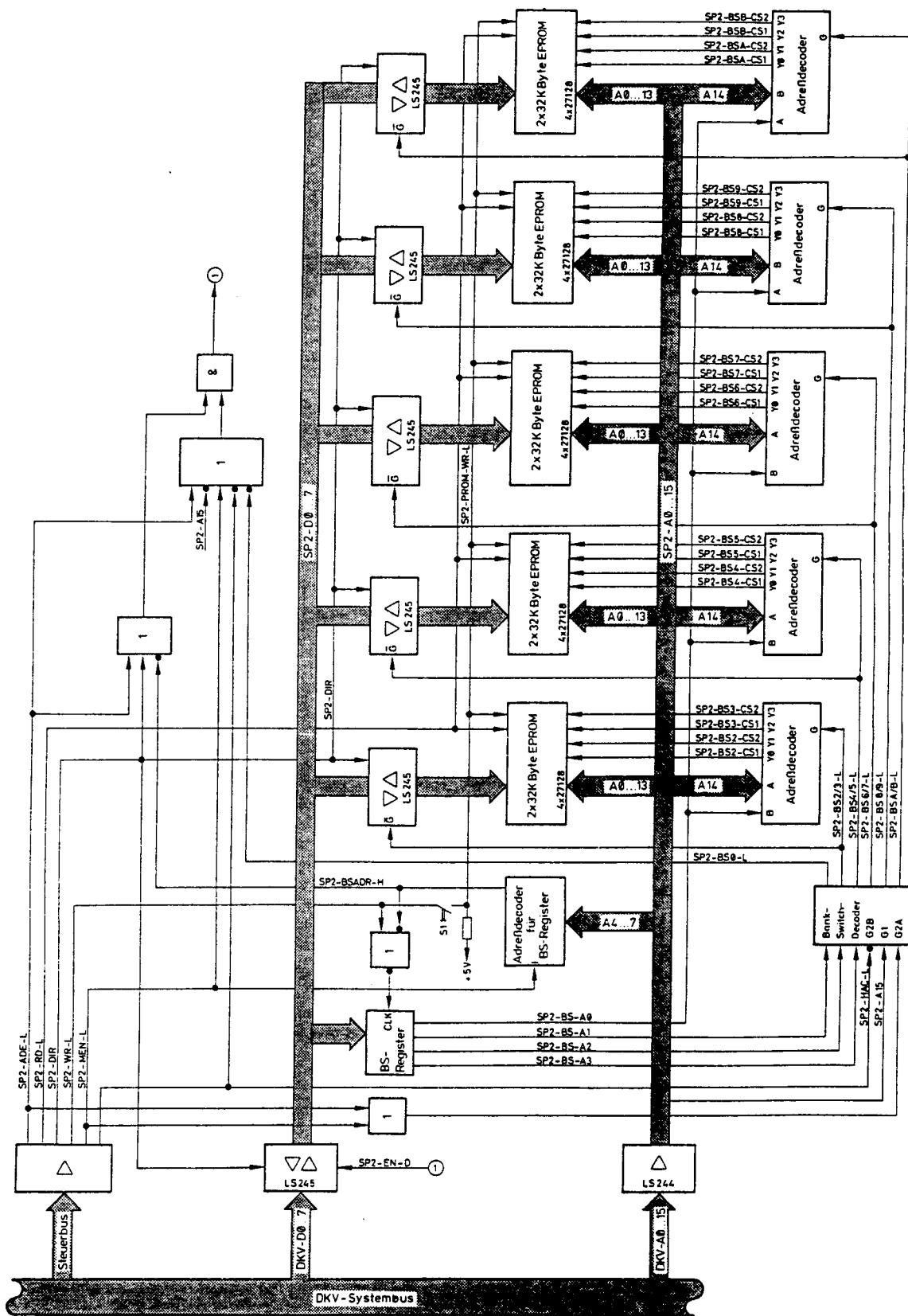

| 3.2.3     | DKV-Speicher 2 S42024-H182-C1 .....                     | 83  |

| 3.2.3.1   | Speicherbänke .....                                     | 83  |

| 3.2.3.2   | Bank-Switch-Decoder .....                               | 83  |

| 3.2.3.3   | Adreßdecoder .....                                      | 83  |

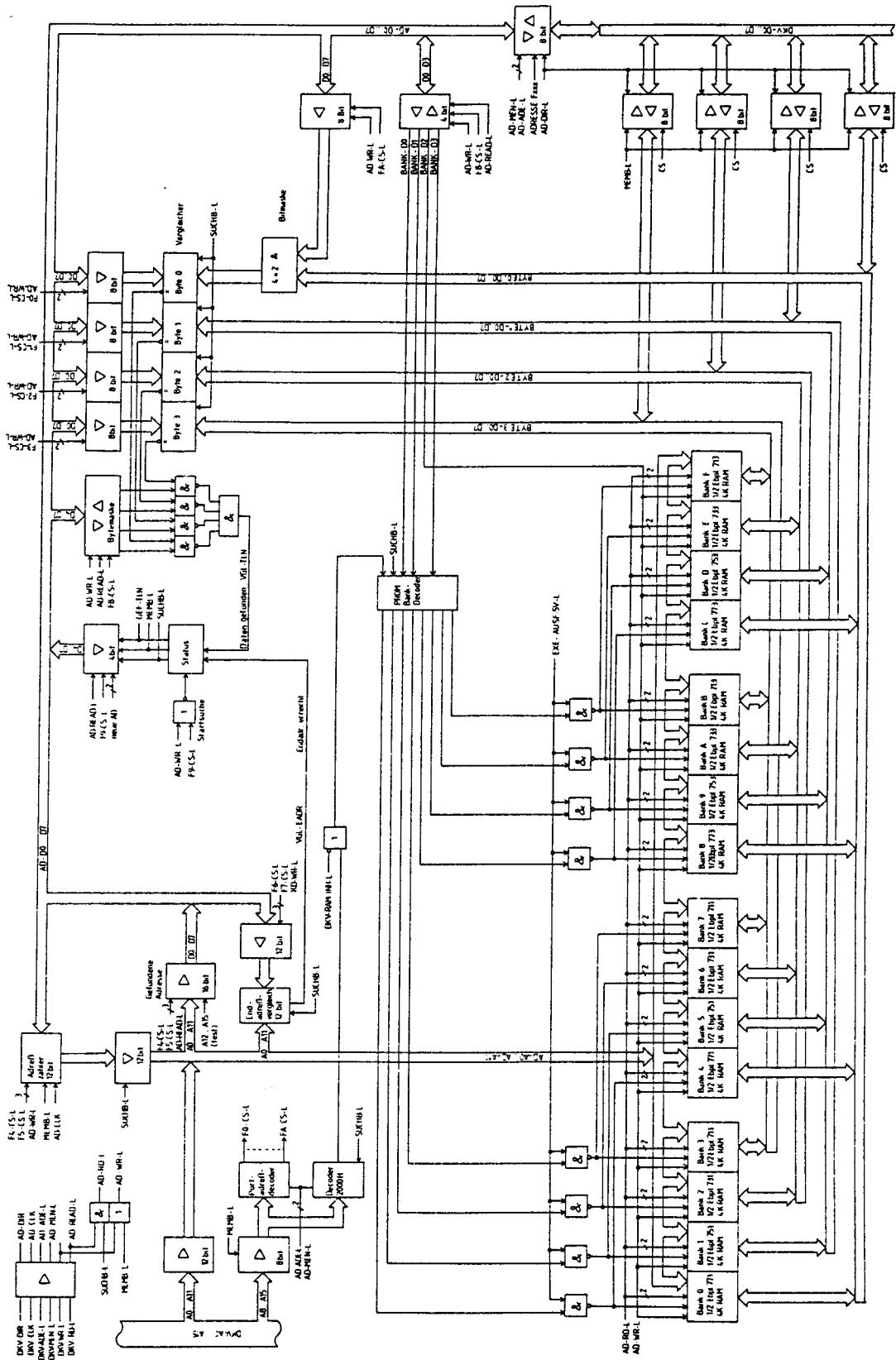

| 3.2.4     | Aktivdatei S42024-H183-E3, -E4 .....                    | 85  |

| 3.2.4.1   | Speicher .....                                          | 85  |

| 3.2.4.2   | Vergleicher .....                                       | 90  |

| 3.2.4.3   | Bank-Switch-Decoder .....                               | 90  |

| 3.2.4.4   | I/O-Adreßdecoder .....                                  | 91  |

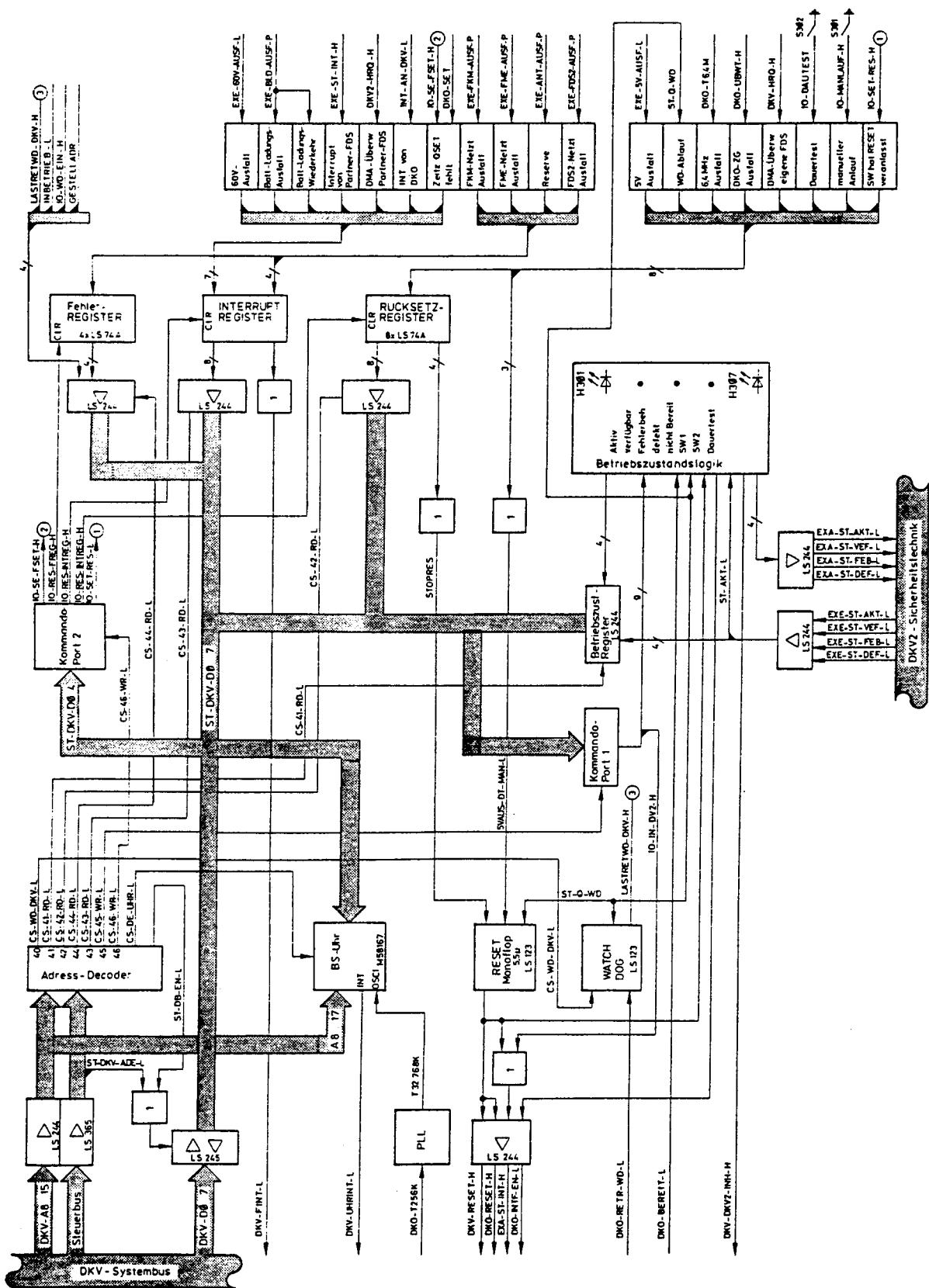

| 3.3       | Sicherheit FDS S42024-H261-E1 .....                     | 95  |

| 3.3.1     | Betriebszustände der Funkdatensteuerung .....           | 97  |

| 3.3.1.1   | Zustand AKTIV .....                                     | 97  |

| 3.3.1.2   | Zustand PASSIV .....                                    | 97  |

| 3.3.1.3   | Zustand VERFÜGBAR .....                                 | 98  |

| 3.3.1.4   | Zustand FEHLERBEHANDLUNG .....                          | 98  |

| 3.3.1.5   | Zustand DEFEKT .....                                    | 98  |

| 3.3.2     | Realisieren der sicherheitstechnischen Funktionen ..... | 98  |

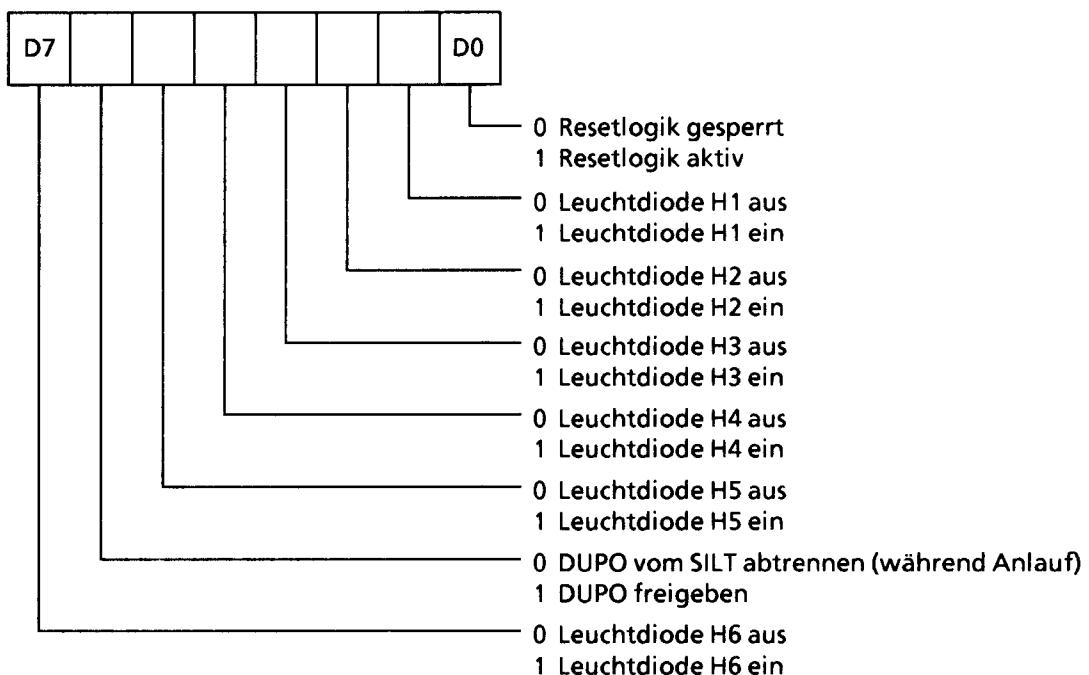

| 3.3.2.1   | Watchdog, Port 40H .....                                | 98  |

| 3.3.2.2   | Lesen der Betriebszustände, Port 41H .....              | 99  |

| 3.3.2.3   | Rücksetzregister, Port 42H .....                        | 100 |

| 3.3.2.4   | Interrupt-Register, Port 43H .....                      | 103 |

|          |                                   |     |

|----------|-----------------------------------|-----|

| 3.3.2.5  | Fehlerregister, Port 44H          | 105 |

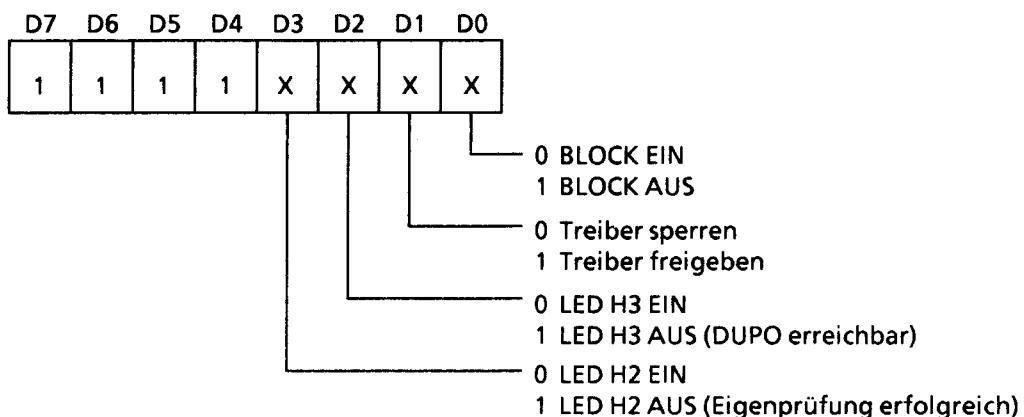

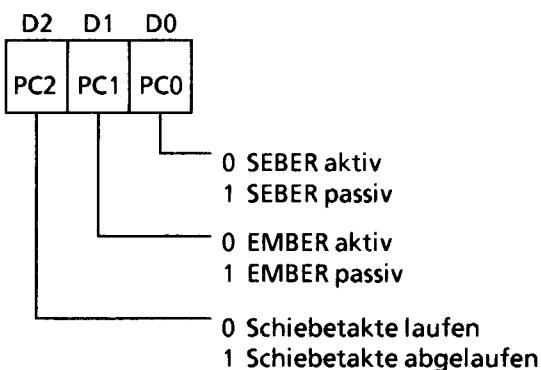

| 3.3.2.6  | Kommando-Port 1, Port 45H         | 106 |

| 3.3.2.7  | Kommando-Port 2, Port 46H         | 108 |

| 3.3.2.8  | Adreßdecoder                      | 109 |

| 3.3.2.9  | Uhr für Basisstation              | 109 |

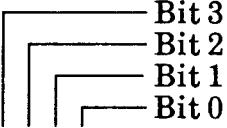

| 3.3.2.10 | Bedienungselemente                | 112 |

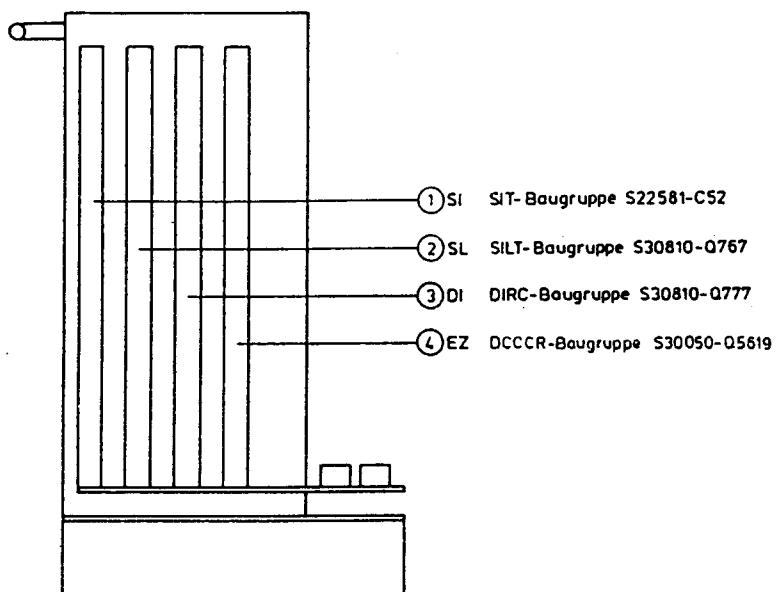

| 4        | Aufbau .....                      | 113 |

| 4.1      | Bestückung .....                  | 113 |

| 4.2      | Technologie und Bauelemente ..... | 114 |

| 5        | Technische Daten .....            | 116 |

| 6        | Geräteübersicht .....             | 117 |

| 7        | Abkürzungen .....                 | 118 |

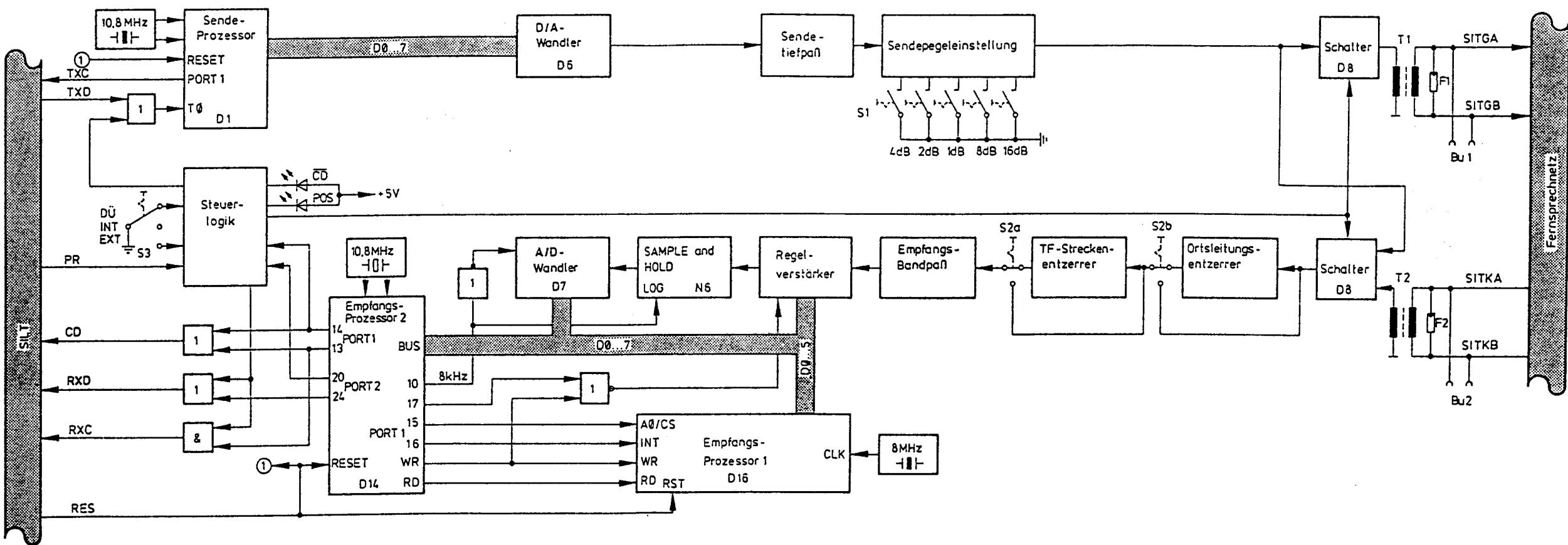

# 1 Übersicht

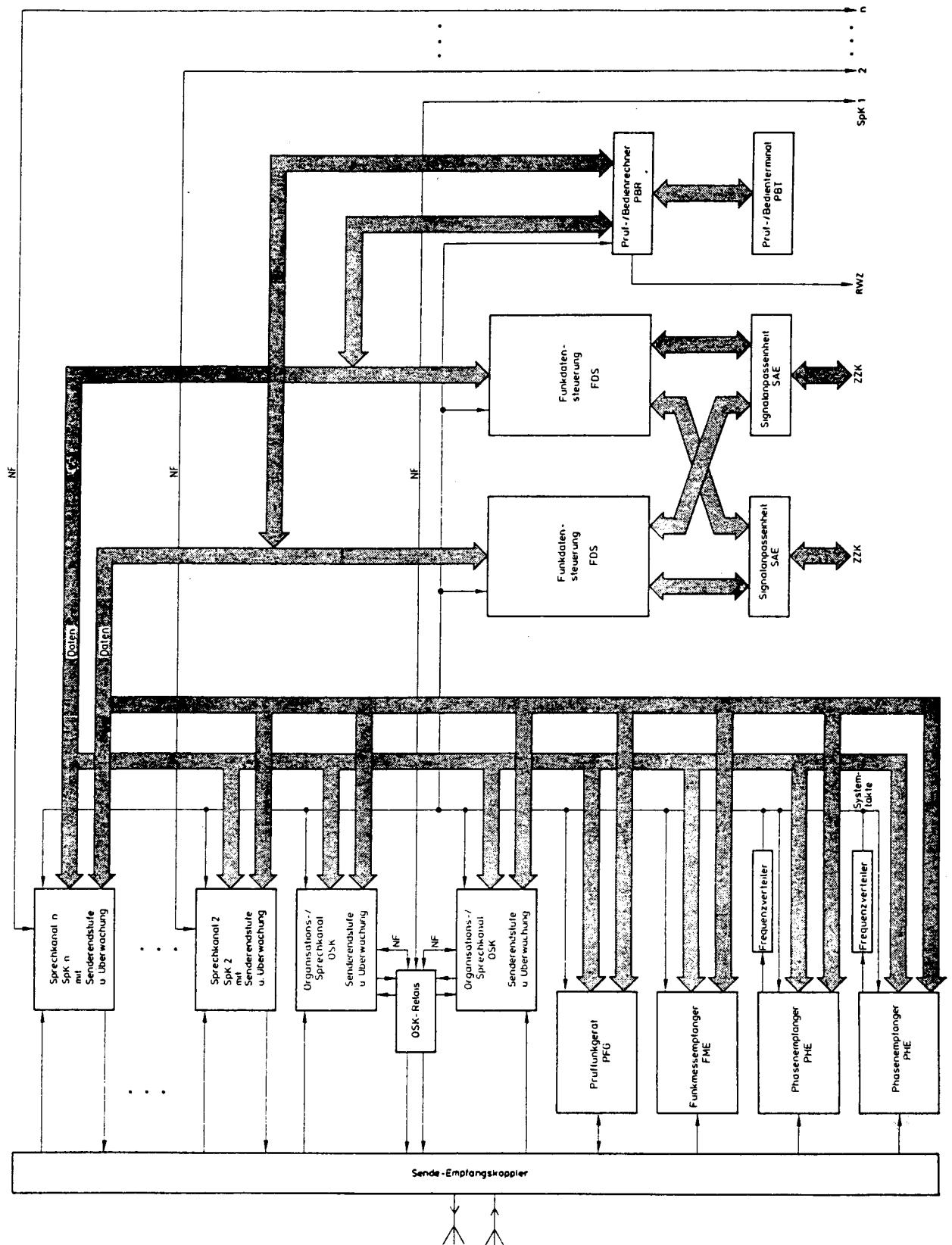

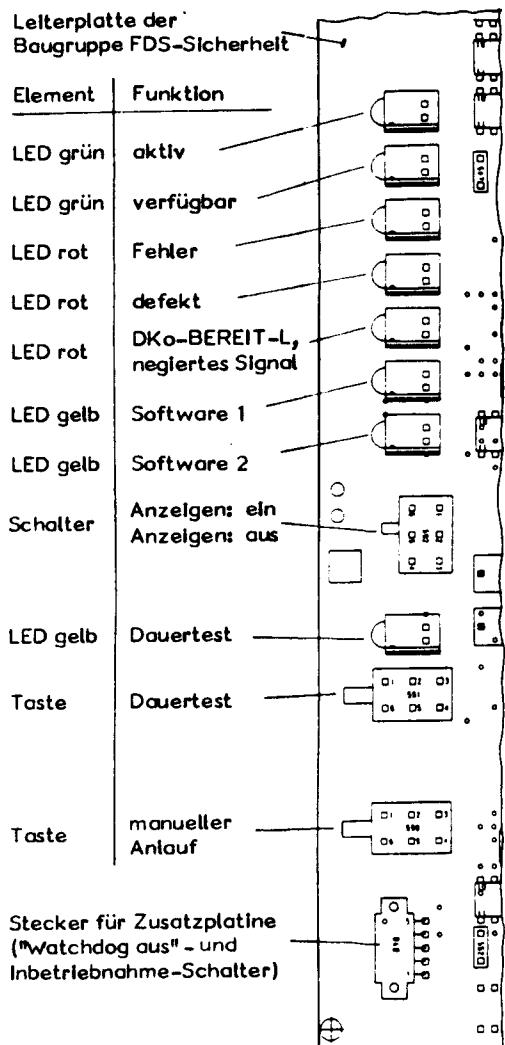

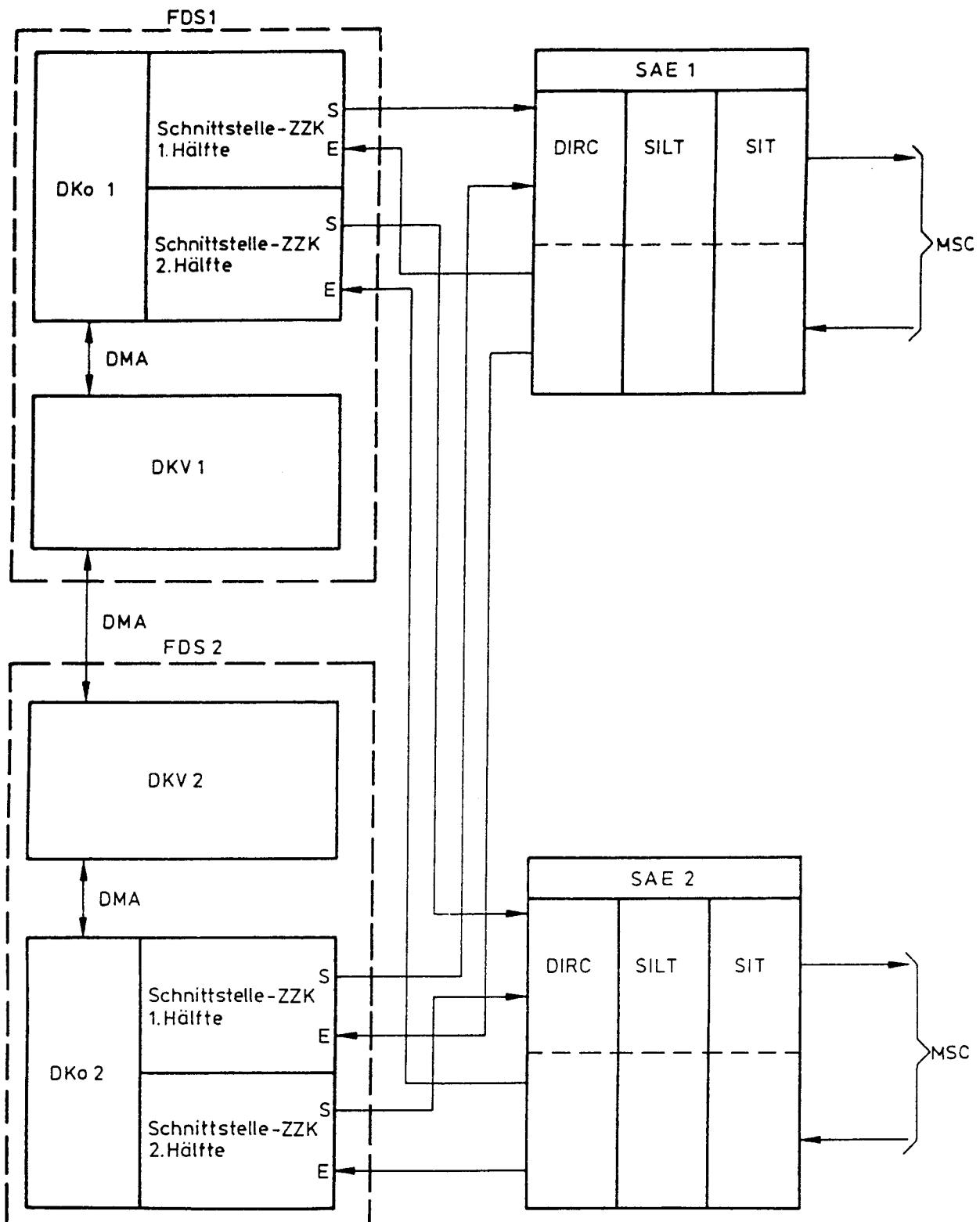

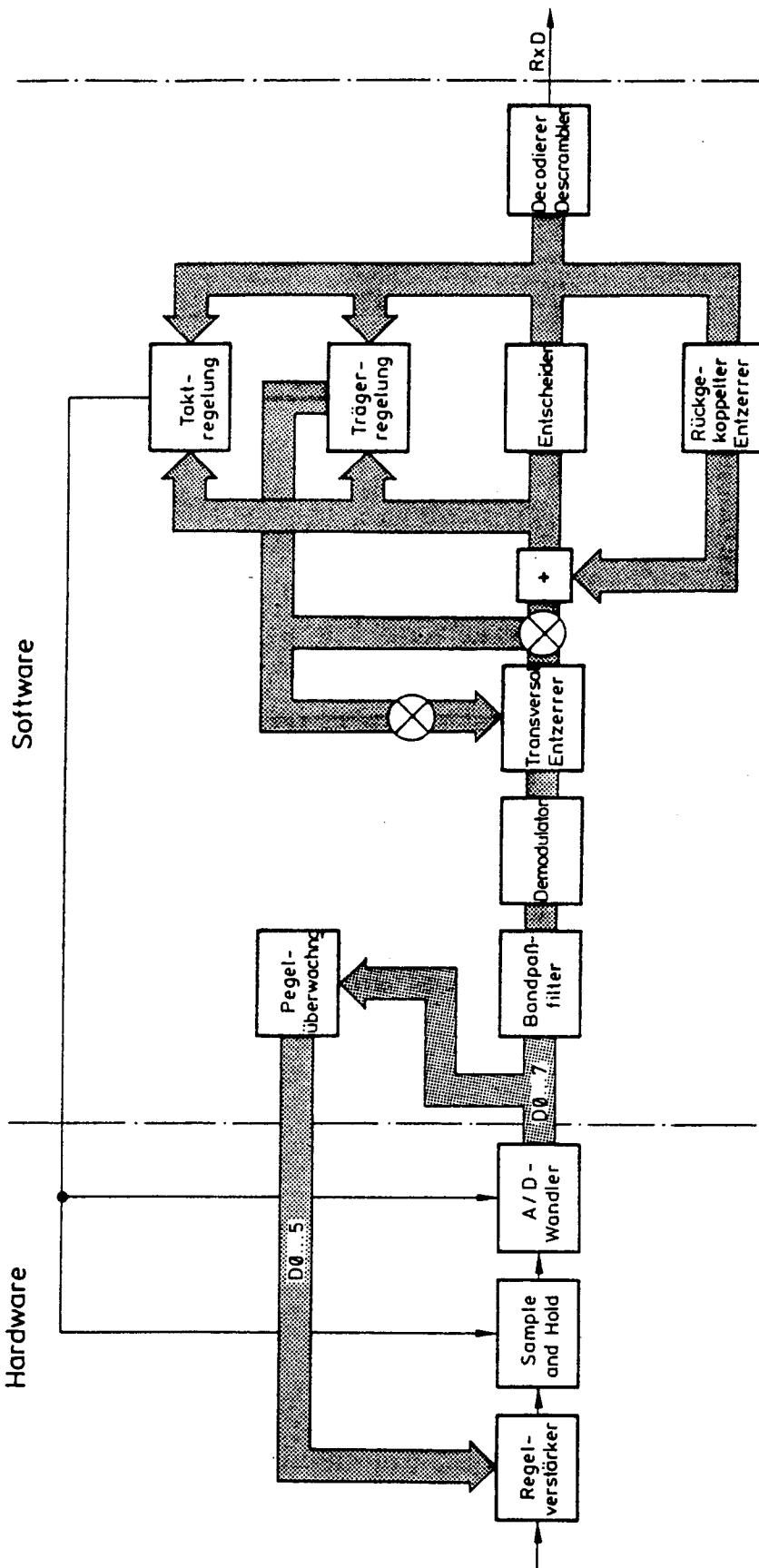

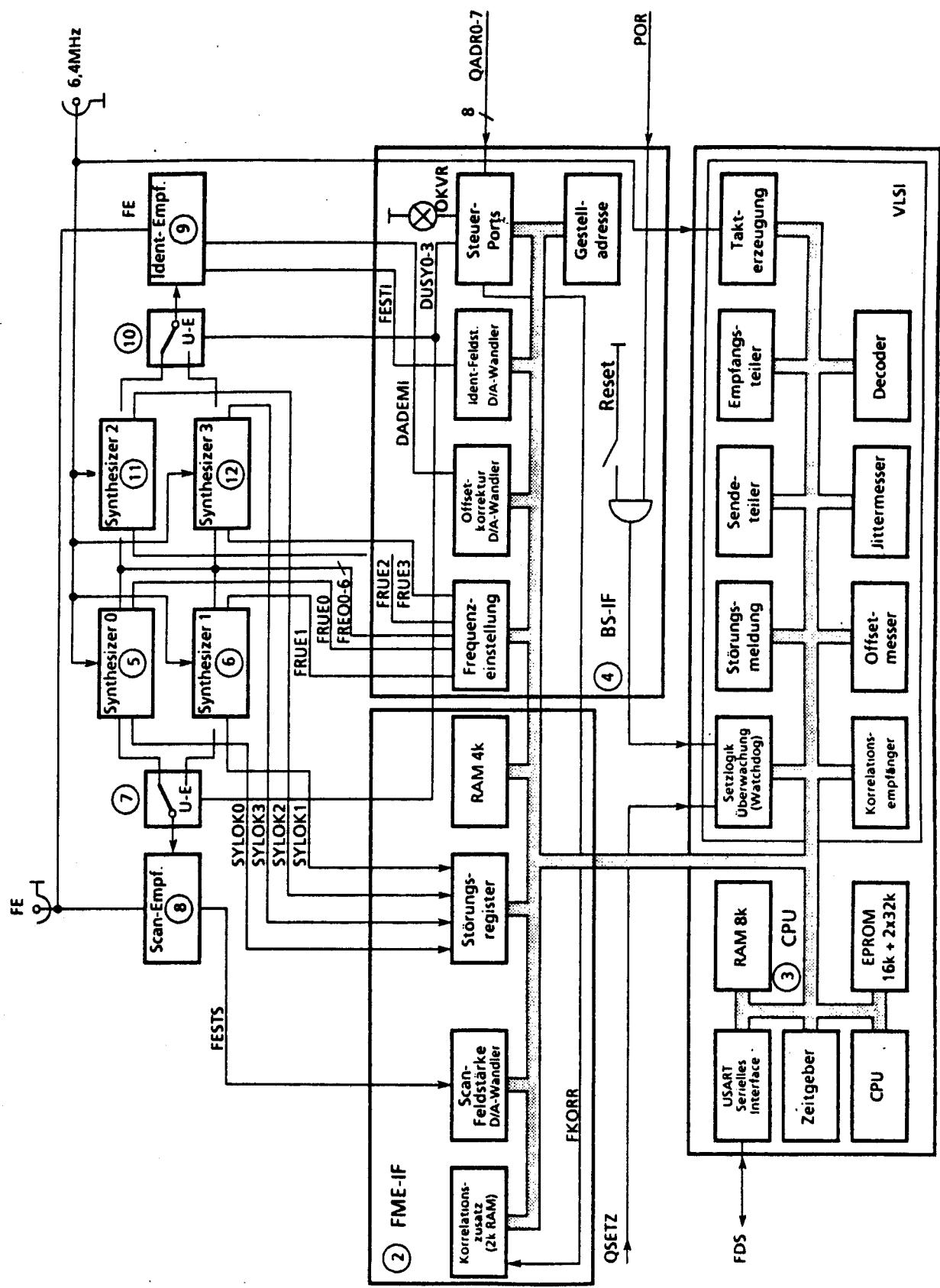

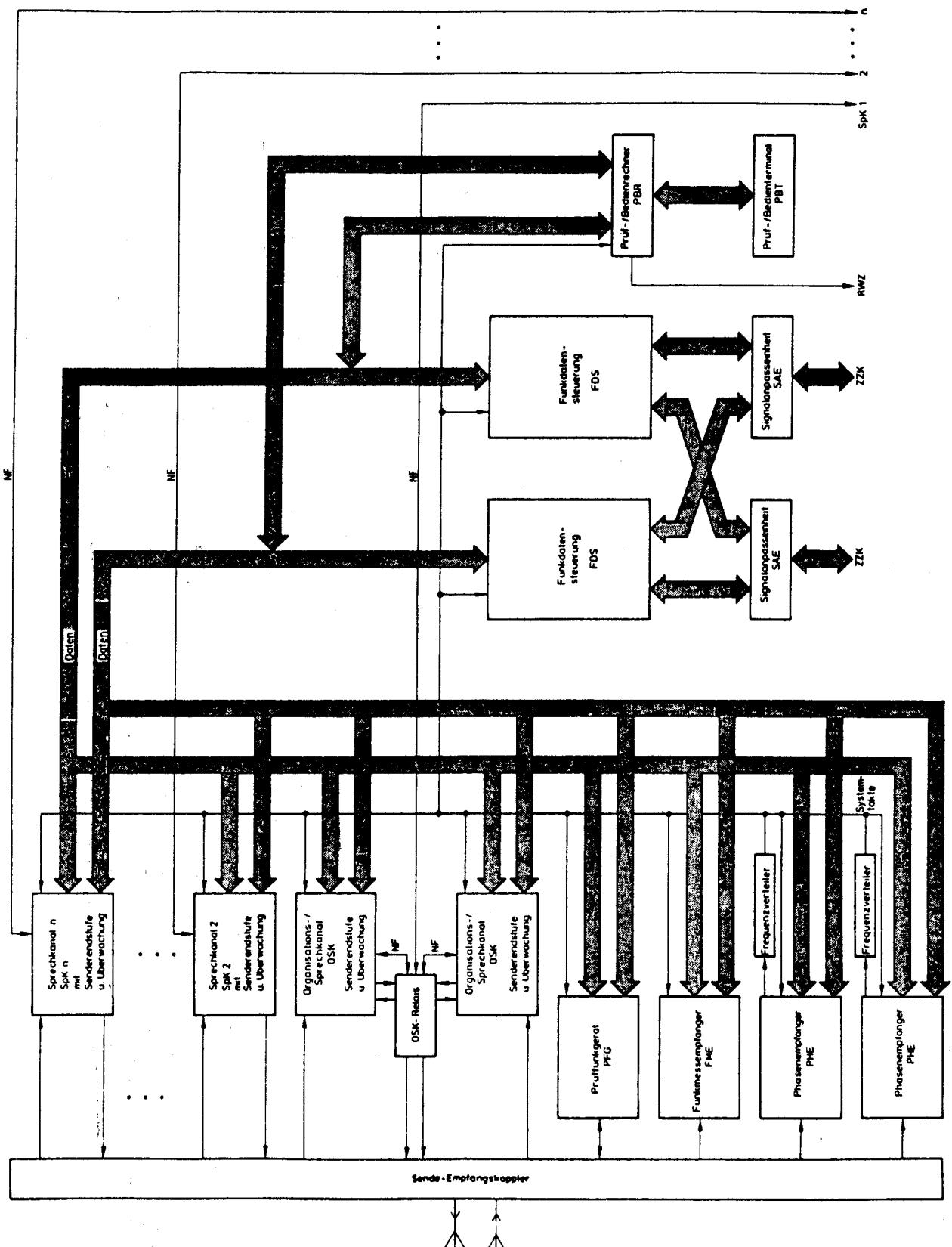

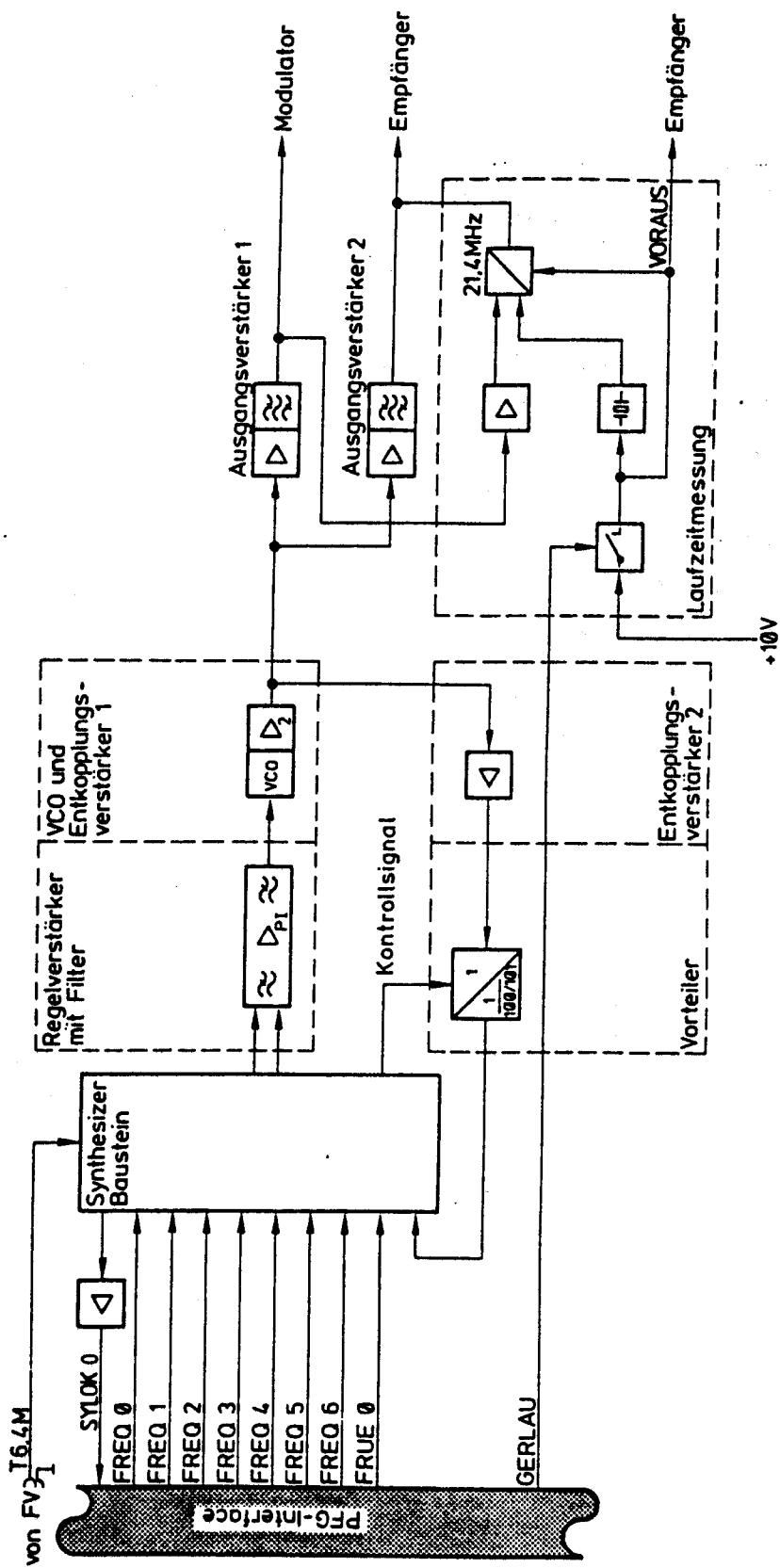

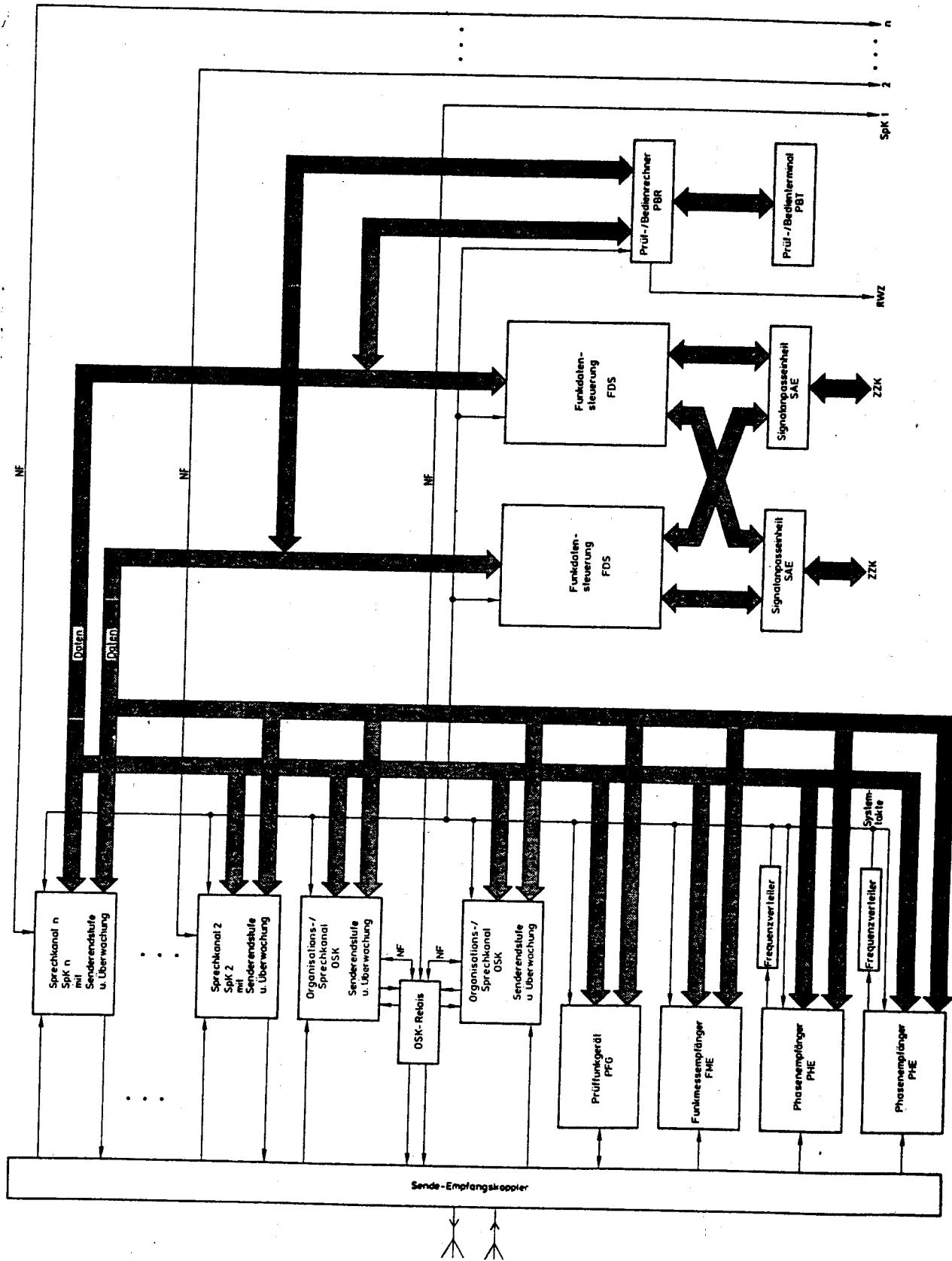

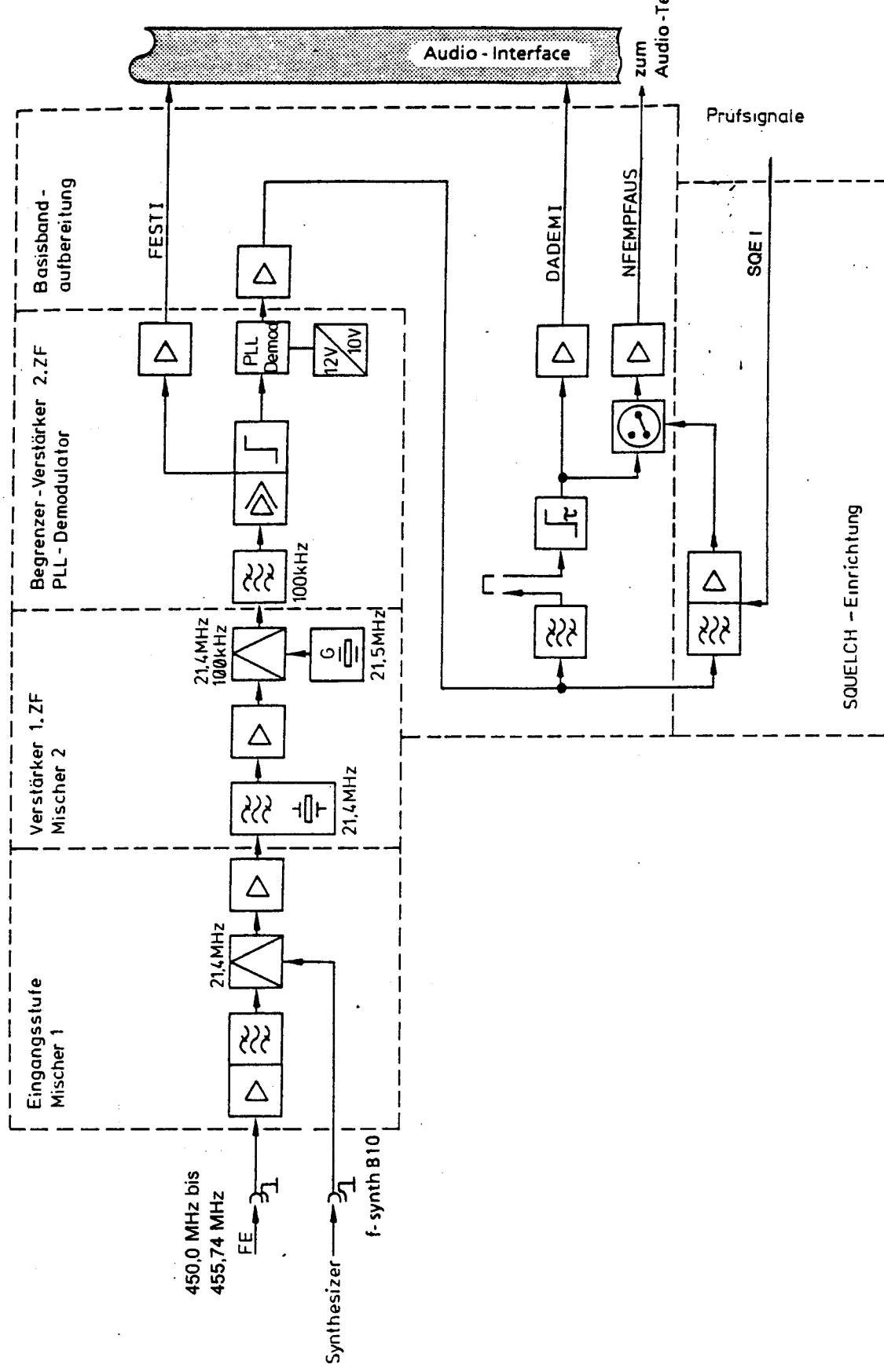

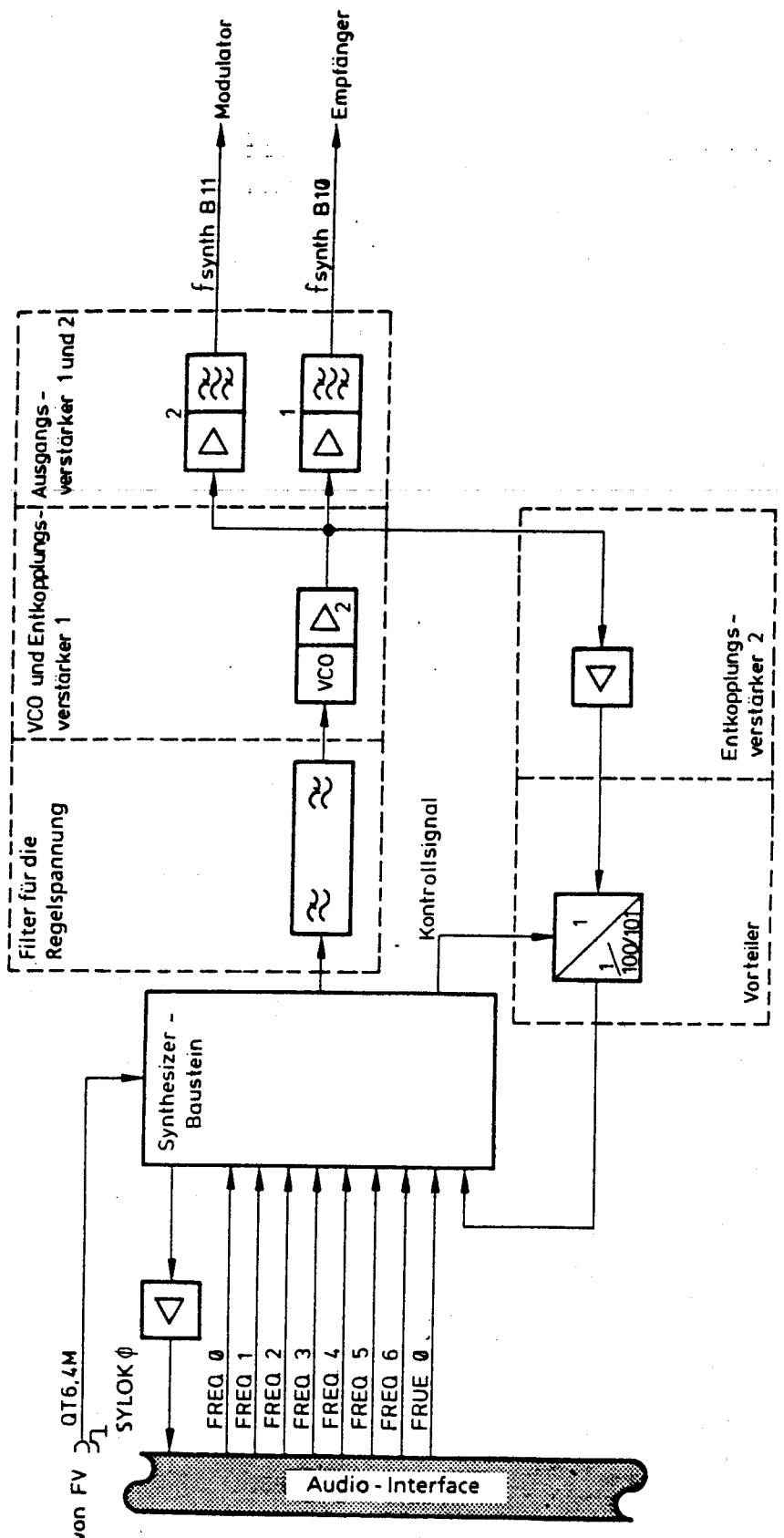

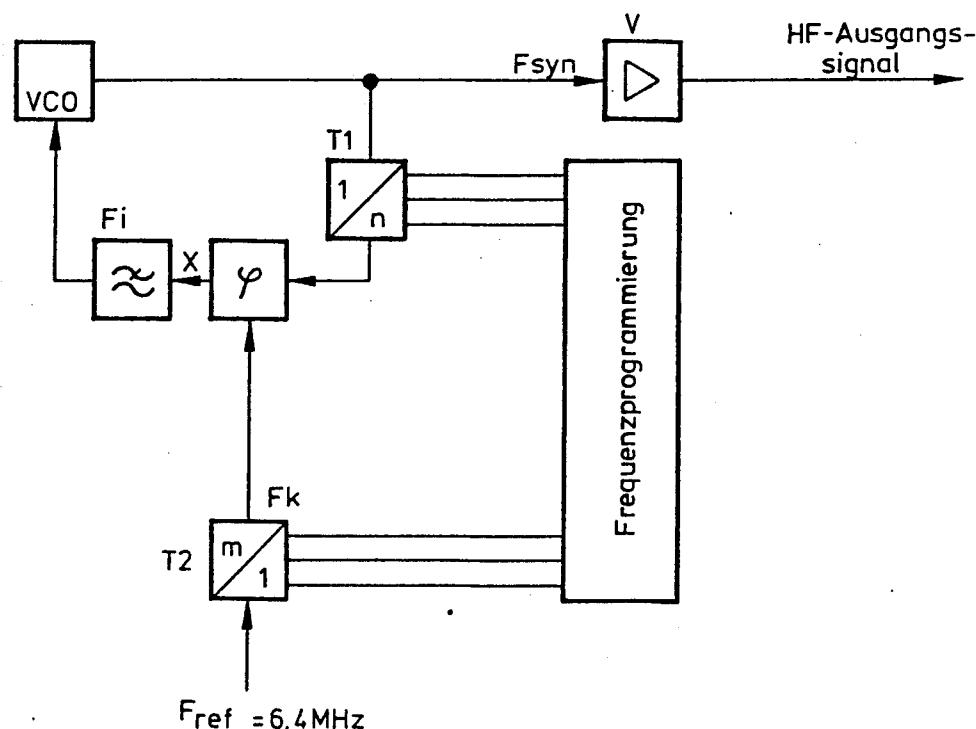

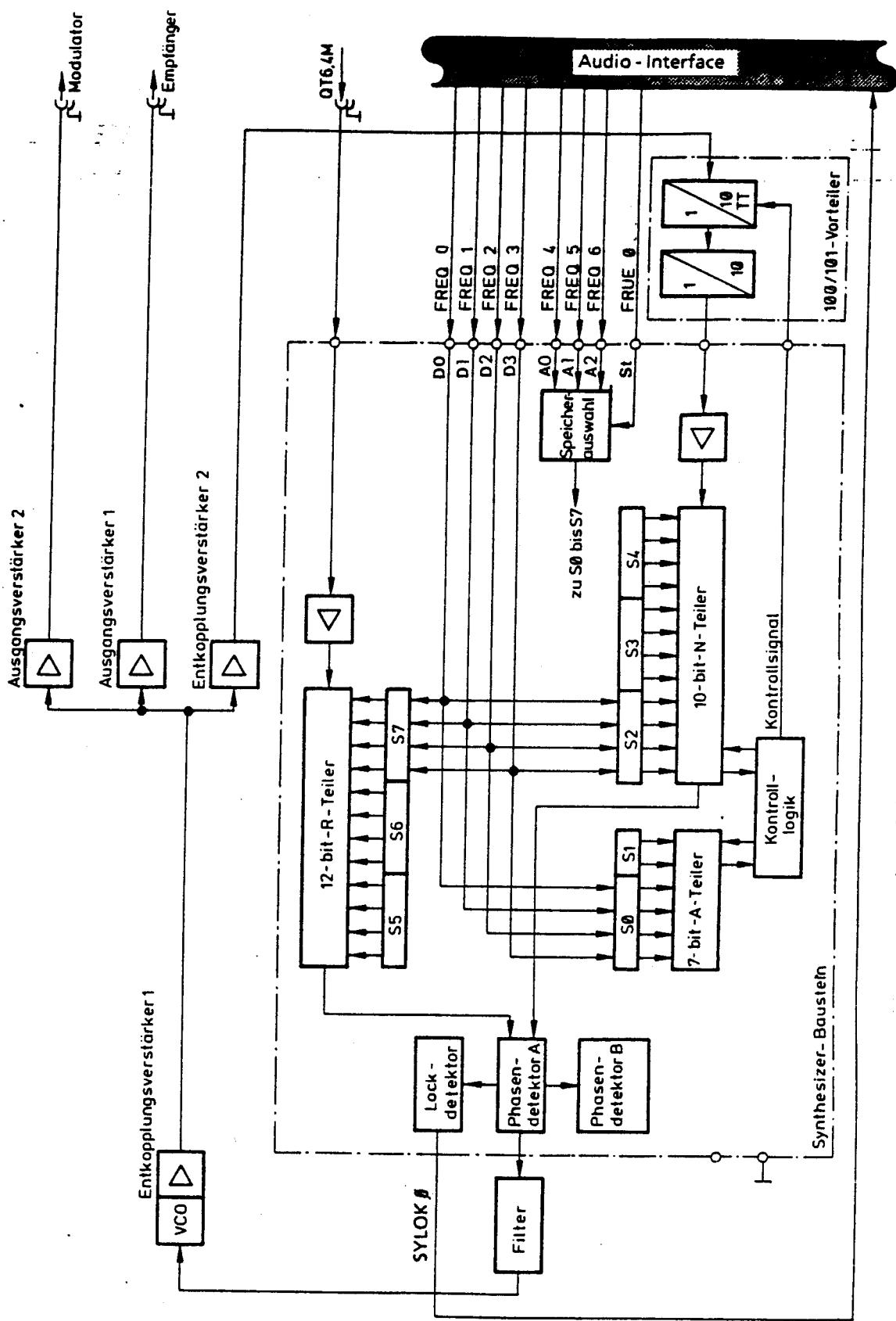

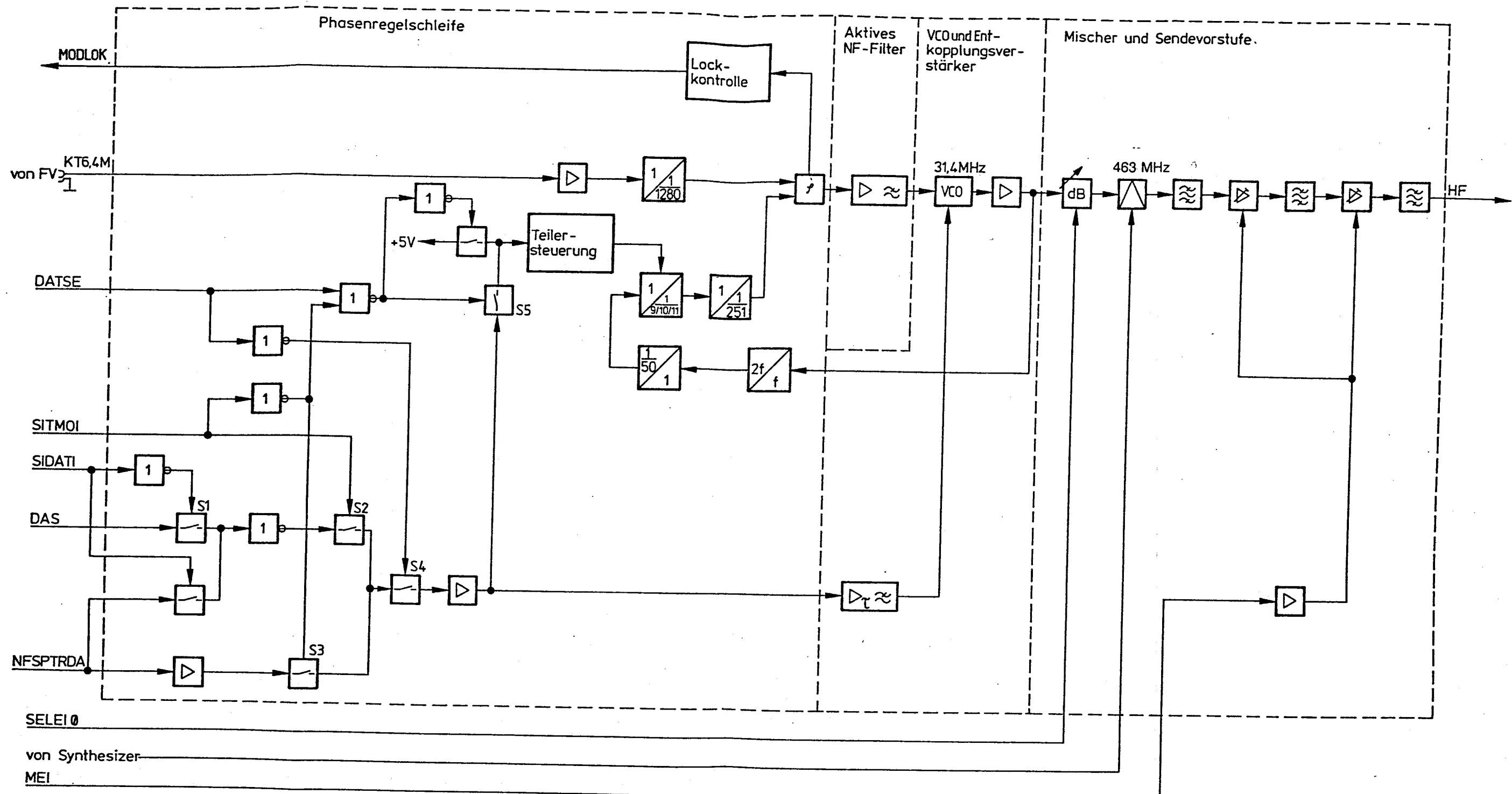

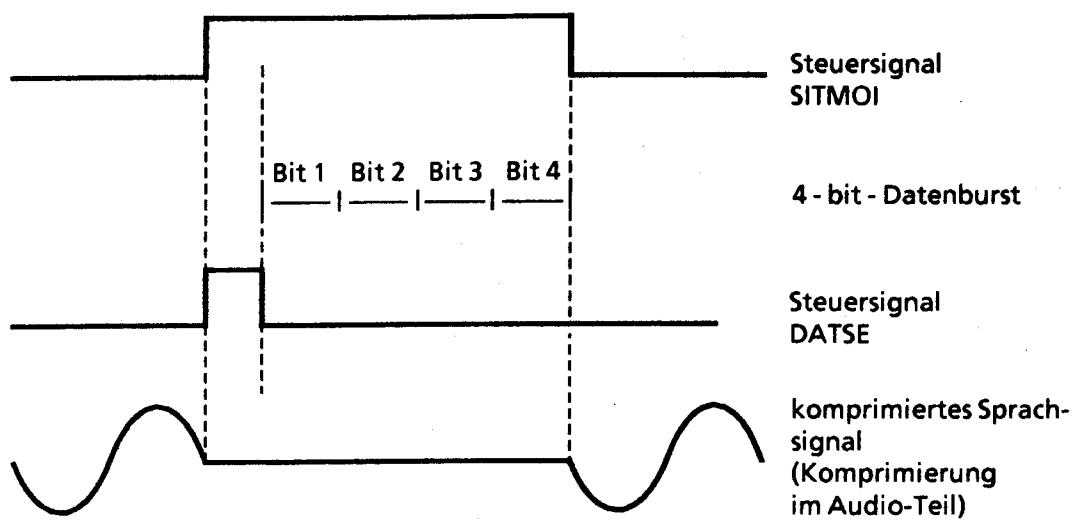

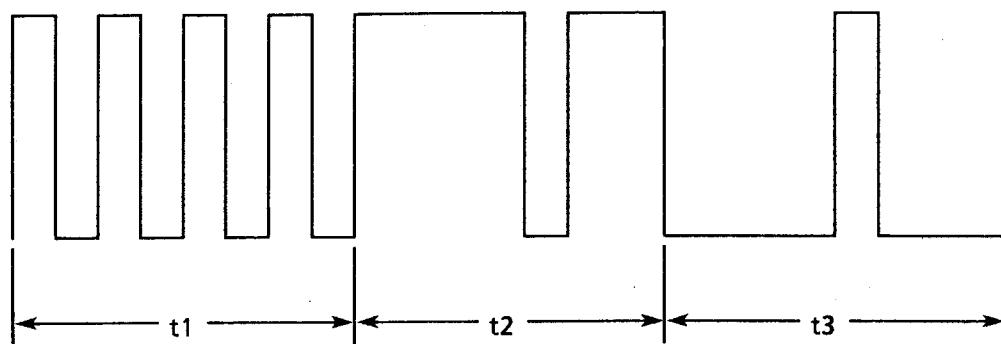

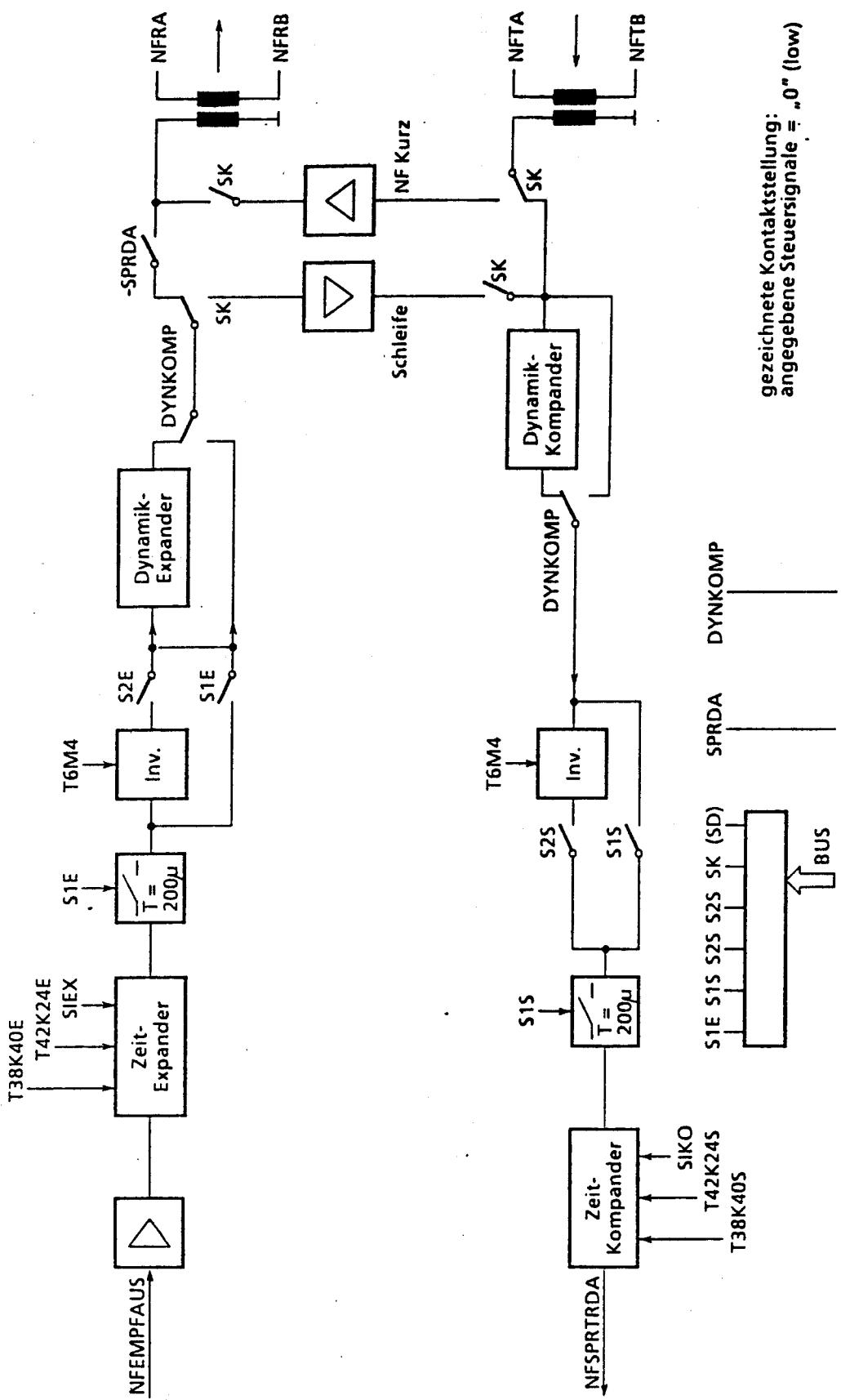

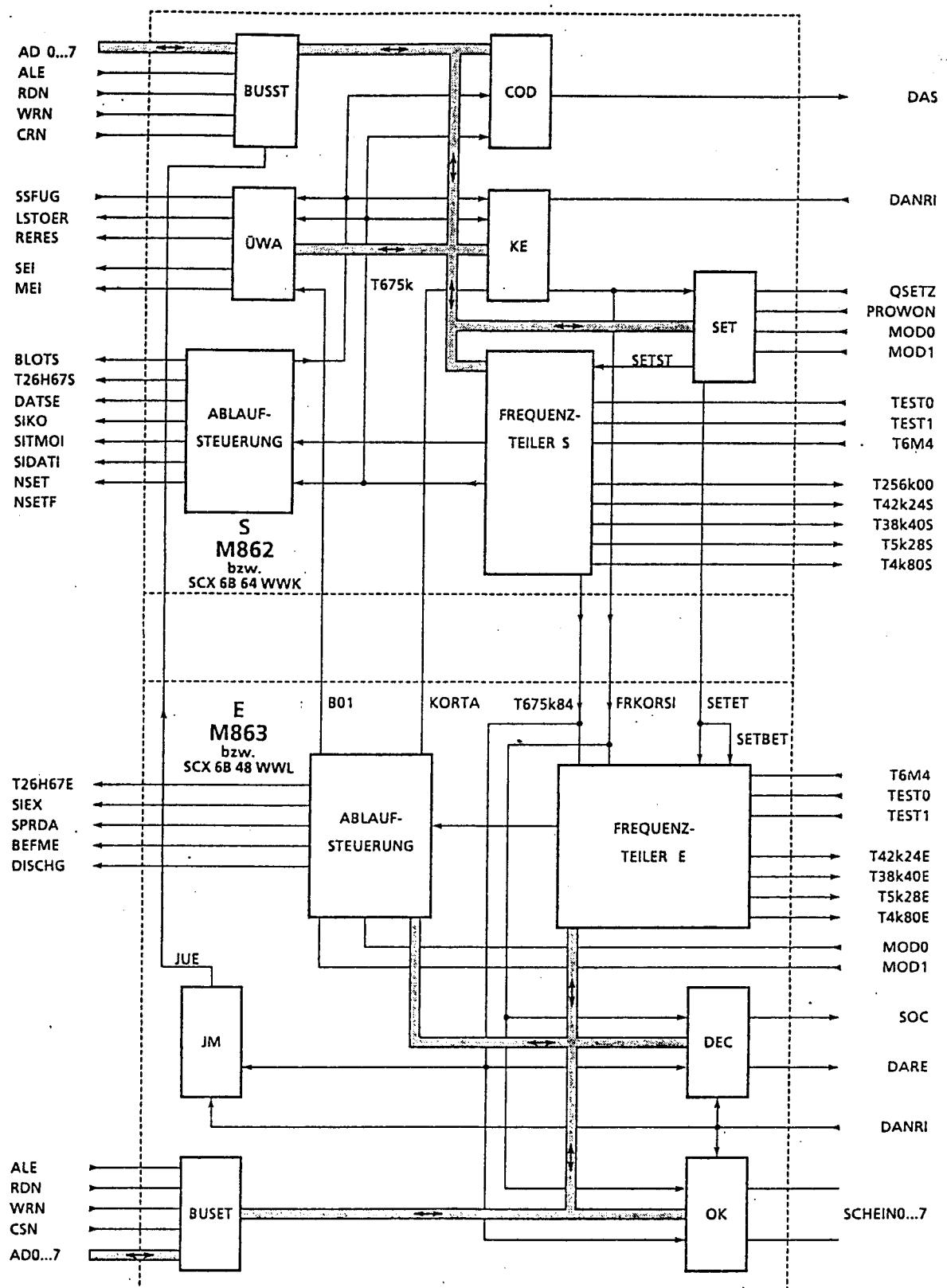

## 1.1 Funkdatensteuerung in der Basisstation (Bild 1)

Die Basisstation (BS) enthält zwei gleichwertige Einsätze Funkdatensteuerung (FDS).

Die beiden Einheiten sind in jeder Hinsicht gleich. In folgender Beschreibung wurde die aktive, also die Betriebs-FDS als FDS1 und die passive Ersatz-FDS (Standby-FDS) als FDS2 definiert.

Es gibt zwei Ausführungen, die sich bezüglich der Datenrettung bei Spannungs-ausfall unterscheiden (siehe Pkt. 3.2.4.1):

- in Ausführung B5 enthält die Baugruppe Aktivdatei zwei ungepufferte RAM-Bausteine für die Anlagenliste

- in der Ausführung B6 sind an dieser Stelle RAM-Bausteine mit eigener Batterie-pufferung zur Datenrettung beim Spannungsausfall verwendet.

Die Funkdatensteuerung ist der zentrale Rechner in der Basisstation des Netzes C 450. Sie verarbeitet und steuert den Datenverkehr von und zum Organisationskanal (OgK), den Sprechkanälen (SpK), dem Phasenempfänger (PHE), dem Funkmessempfänger (FME) und dem Prüffunkgerät (PFG).

Die Verarbeitung wird im Echtzeitbetrieb vorgenommen. Die Synchronisiersignale sind das Setzsignal (QSET) und der Takt (6,4 MHz). An der FDS ist weiterhin ein Prüf-/Bedienrechner (PBR) mit einem Prüf-/Bedienterminal (PBT) angeschlossen. Die Verbindung zur Funkvermittlungsstelle (MSC) wird über die Signalanpaßeinheit (SAE) und den Zentralen Zeichengabekanal (ZZK) hergestellt.

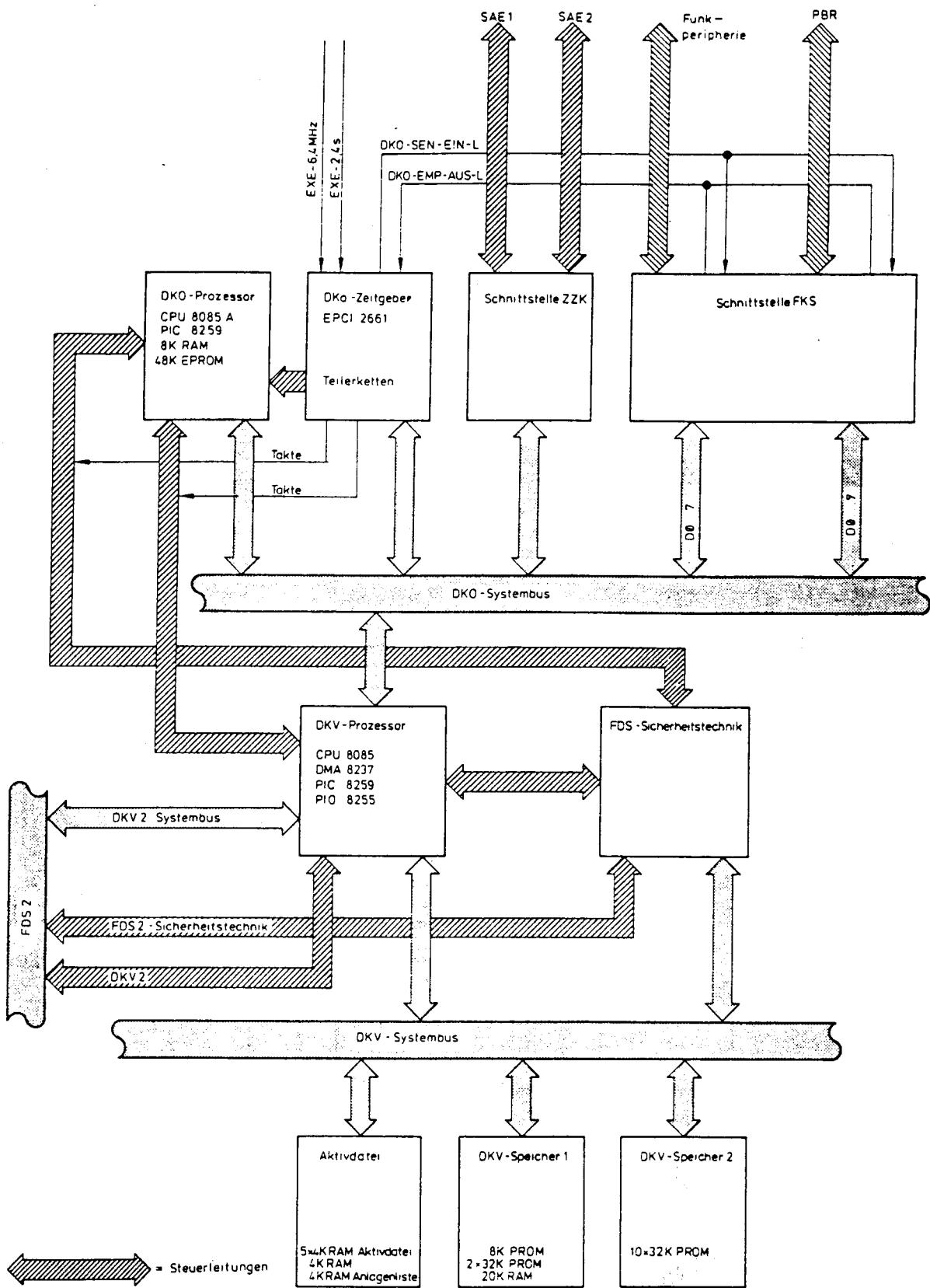

Die Funkdatensteuerung gliedert sich in Dateien- und Kanalverwaltung (DKV) und Datenkonzentrator (DKo).

Die Dateien- und Kanalverwaltung (DKV) ist der Zentralrechner in der Funkdatensteuerung. Dieser verarbeitet Meldungen der angeschlossenen Geräte, die ihm über den Datenkonzentrator (DKo) geliefert werden und gibt Meldungen zurück. Dadurch nimmt die Dateien- und Kanalverwaltung die nachfolgenden aufgeführten Aufgaben der FDS wahr. Die DKV führt außerdem auch den DMA-Transfer zum DKo durch.

Der Datenkonzentrator ist der Schnittstellenrechner der Funkdatensteuerung. Er konzentriert die Schnittstellensignale der angeschlossenen Geräte zu Meldungen, die über DMA in die DKV übertragen werden und umgekehrt. Der DKo bedient folgende Schnittstellen:

- Serielle Schnittstelle (256 kBaud) zur Funkperipherie und zum PBR.

- Serielle Schnittstelle zur SAE (ZZK zur MSC). Level 3 des ZZK System 7 (Netzorganisation des ZZK-Netzwerkes, Kontrolle der Ersatzschaltung im Fehlerfall zwischen den beiden SAE, Aufteilung der Meldungen auf die beiden SAE und Ausgabe von Störungsmeldungen).

- Meldungspuffer im RAM (DMA-Schnittstelle zur DKV).

Außerdem übernimmt der Datenkonzentrator die Taktzeugung für die Funkdatensteuerung.

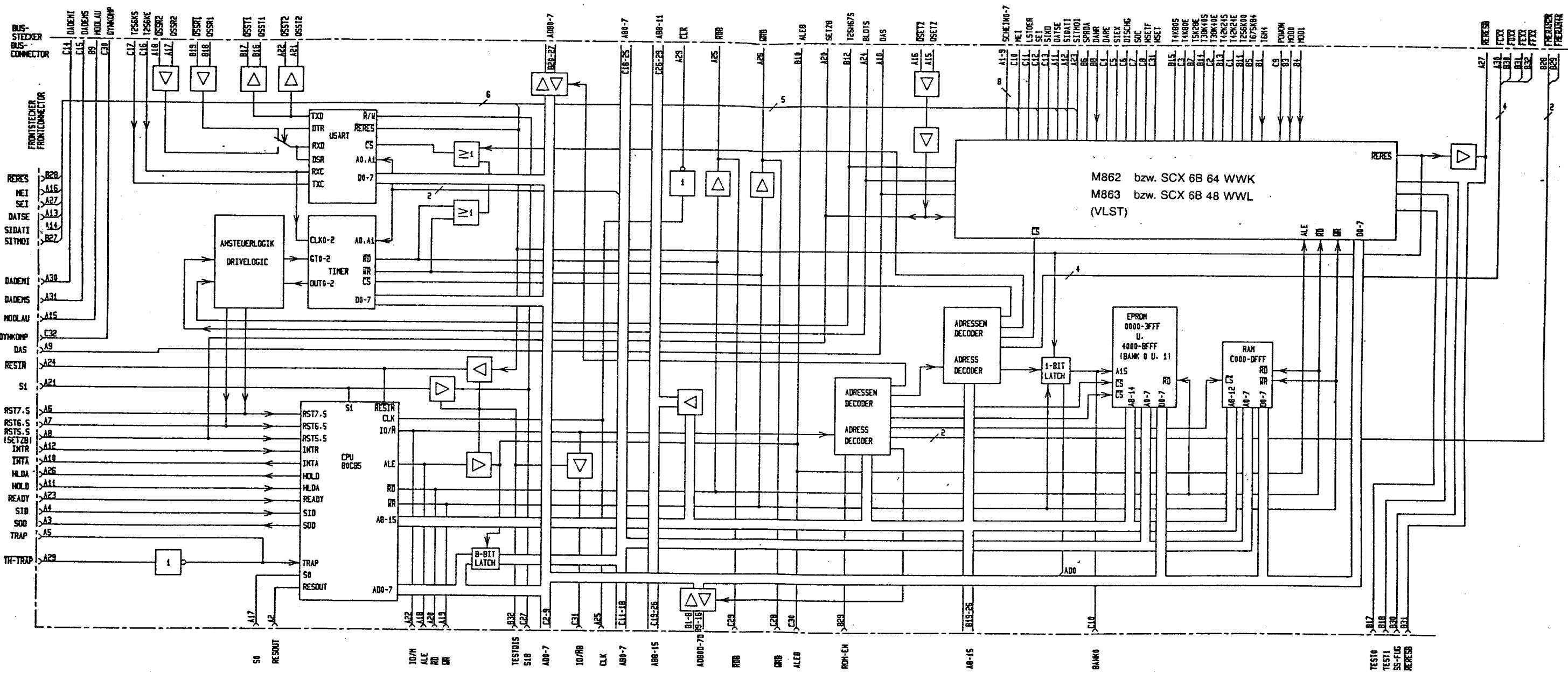

Bild 1 Übersichtsschaltplan einer Basisstation

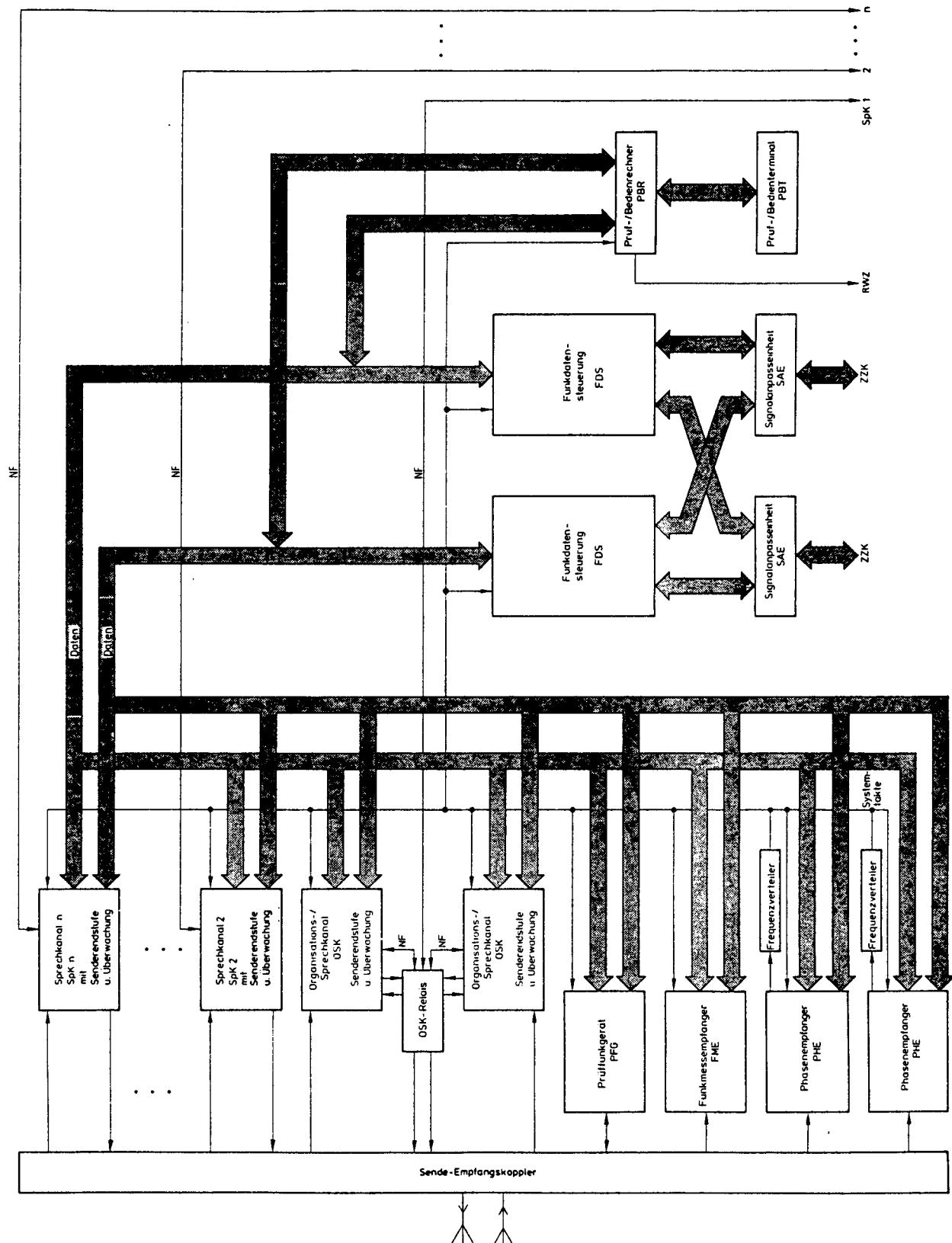

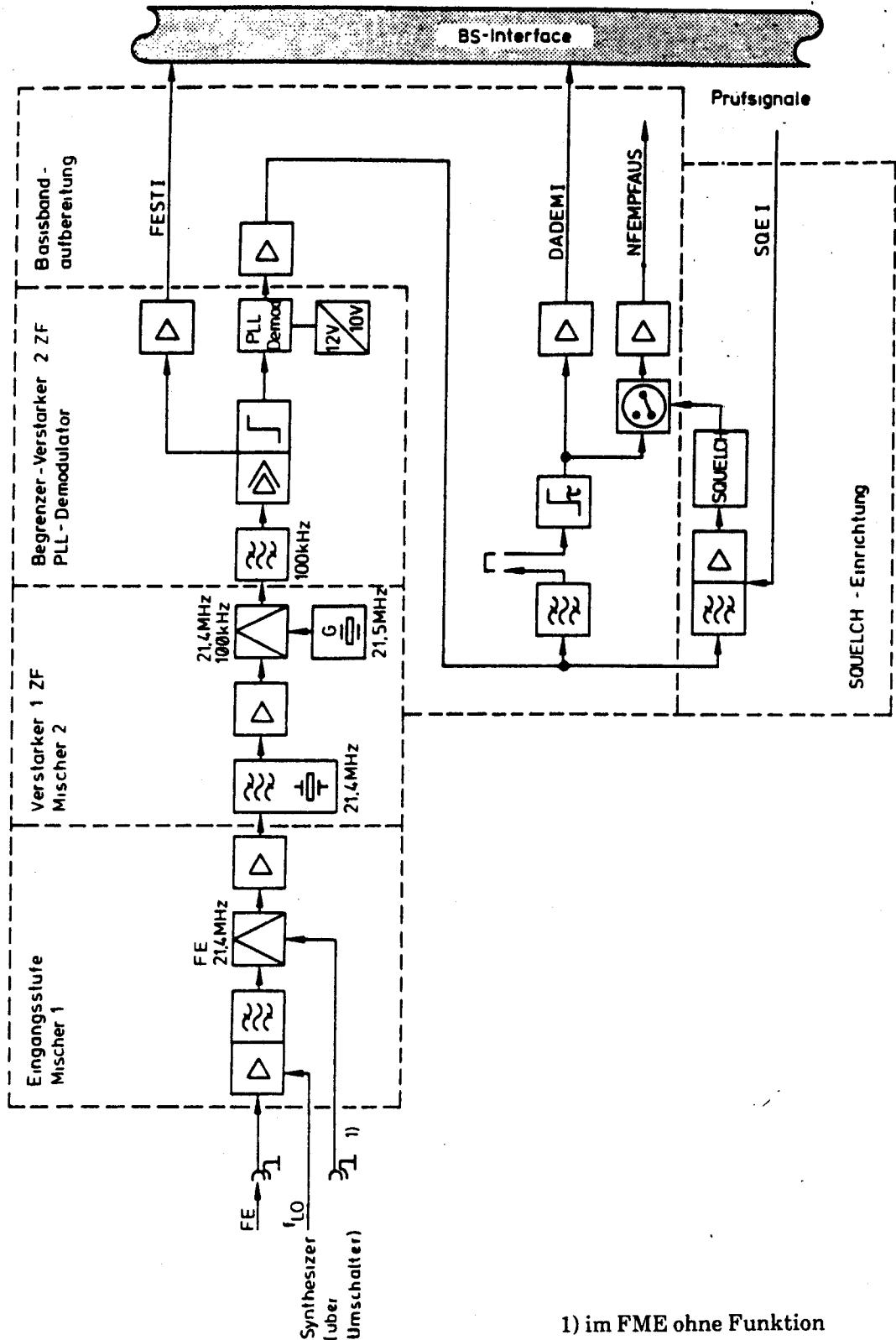

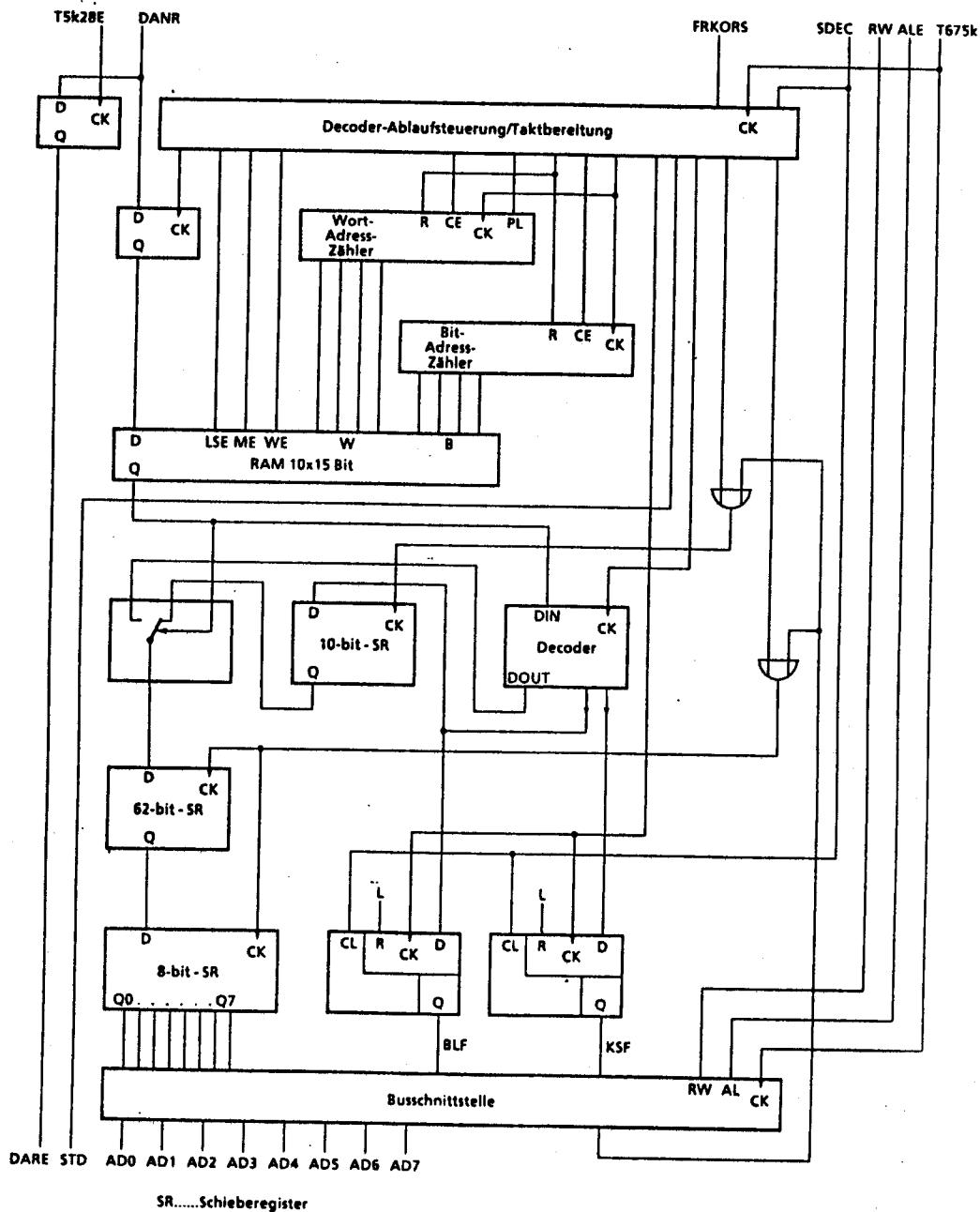

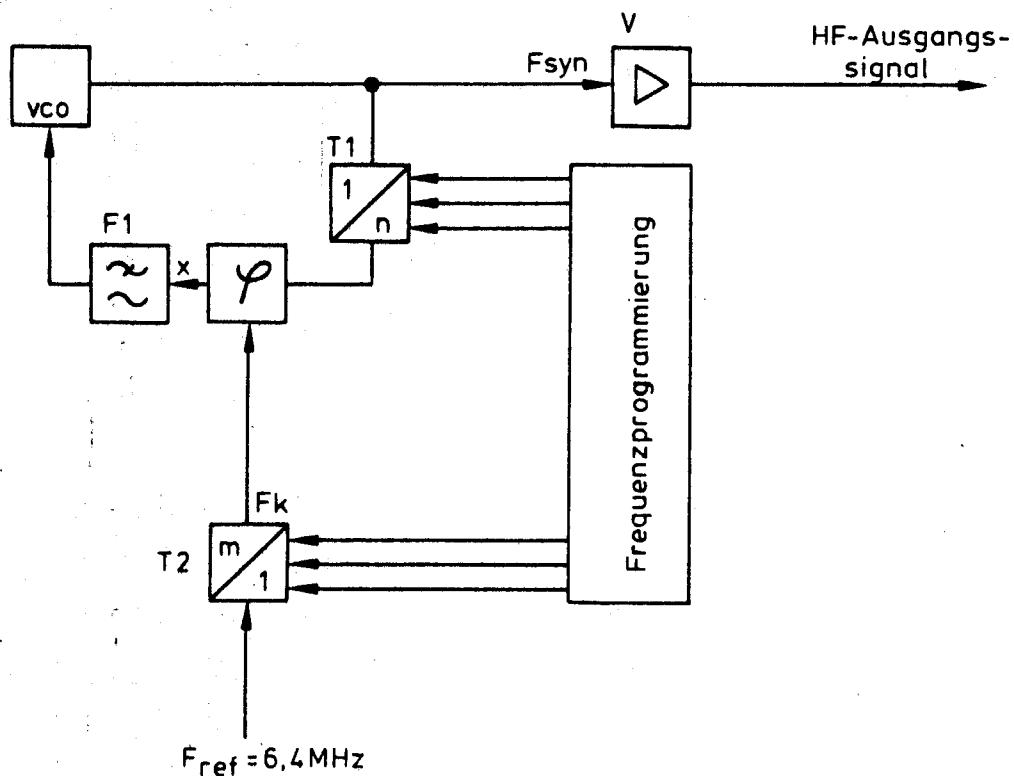

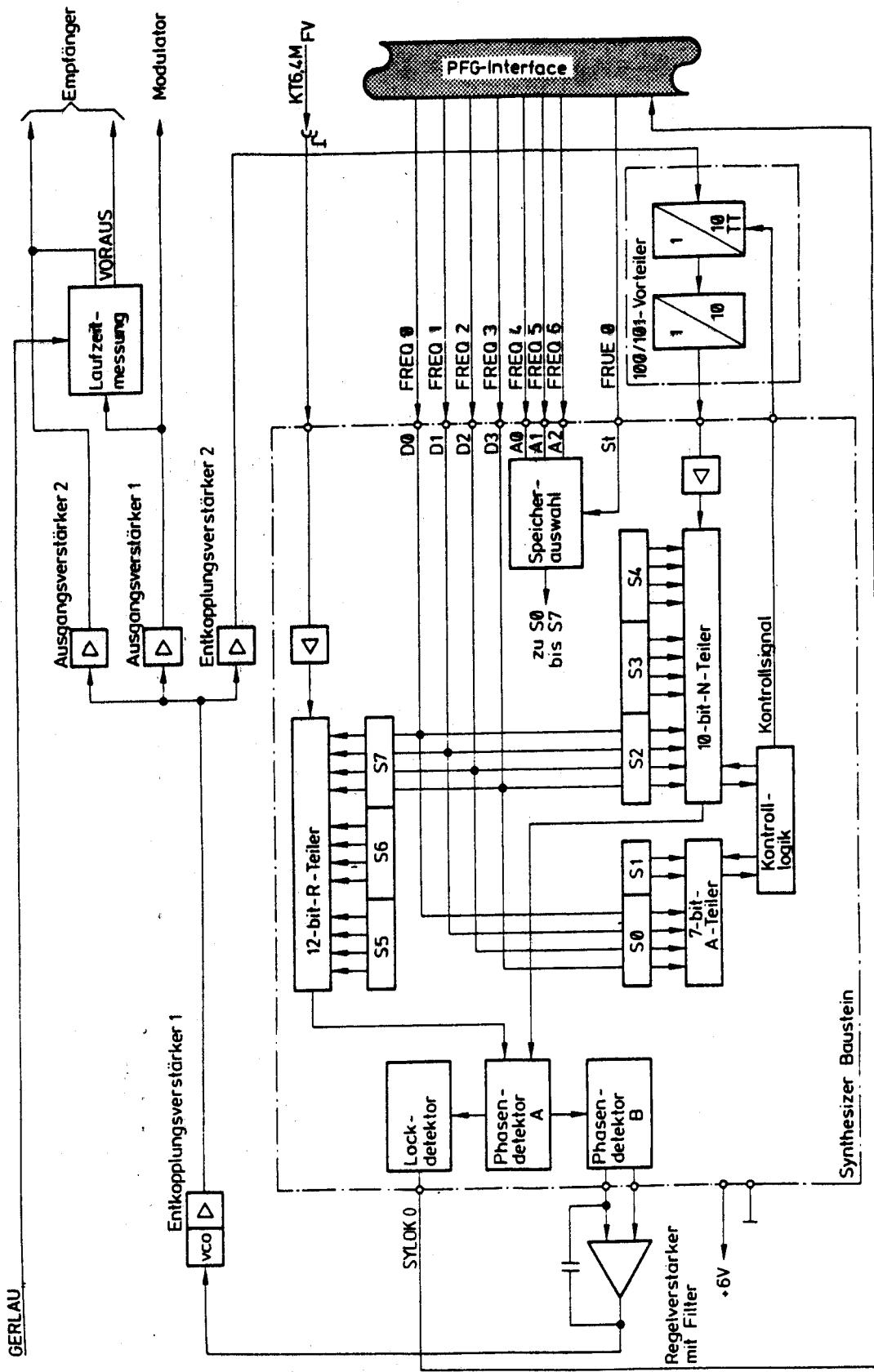

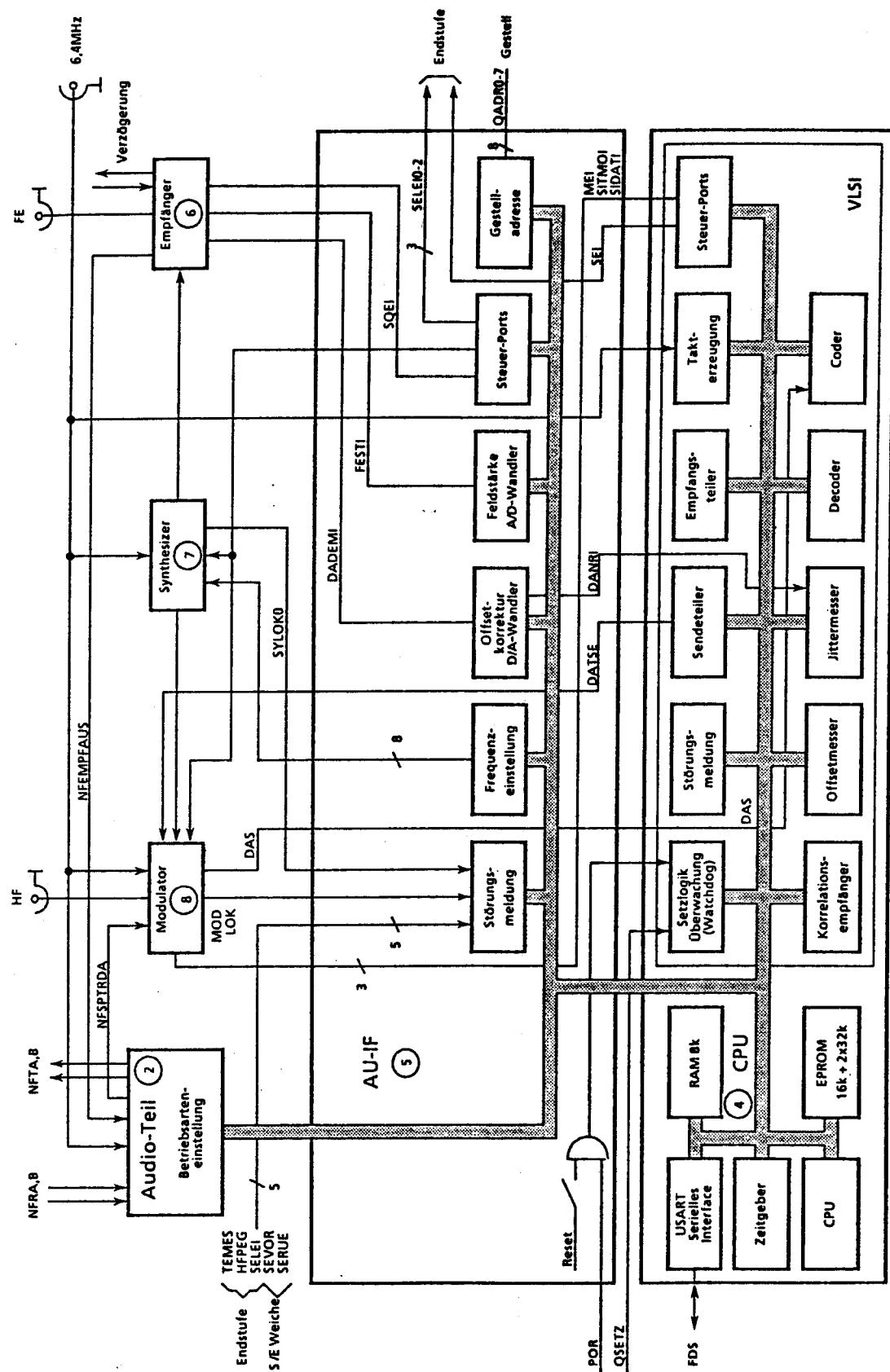

Bild 2 Übersichtsschaltplan der Funkdatensteuerung (FDS)

## **1.2 Aufgabenstellung**

### **1.2.1 Betriebstechnische Aufgaben**

Die Funkdatensteuerung hat in der Basisstation die Aufgabe die Anlagendaten zu verwalten und auszugeben.

### **1.2.2 Vermittlungstechnische Aufgaben**

Für die Vermittlung übernimmt die Funkdatensteuerung folgende Funktionen:

- Einbuchen von Teilnehmern

- Umbuchen von Teilnehmern

- Ausbuchen von Teilnehmern

- Meldezyklus (zyklischer Aufruf der eingebuchten Teilnehmer)

- Gehender und kommender Verbindungsaufbau

- Gesprächsumschaltung (Umschalten von Sprechkanälen während des Gesprächs)

- Warteschlangenbetrieb.

### **1.2.3 Sicherheitstechnische Aufgaben**

Die Funkdatensteuerung ist aus sicherheitstechnischen Gründen (Verfügbarkeit) doppelt vorhanden. Nur die aktive FDS1 bedient die Schnittstellen. Die sicherheitstechnischen Aufgaben sind:

- Wiederanläufe von FDS und Funkperipherie

- Aktiv/passiv-Umschaltung

- Verwalten der weiteren Betriebszustände

- Fehlererkennung und -behandlung (Hardware- und Softwarefehler)

- Überwachen der Systemtakte

- Überwachen der Stromversorgungen in der Basisstation

- Prüfen der Funkperipherie durch Interfaceprüfung

- Melden der Fehler oder des Defektzustands der passiven FDS2 über PBR oder an die MSC.

#### **1.2.4 Funktechnische Aufgaben**

Um die Übertragungsgüte zu gewährleisten, realisiert die Funkdatensteuerung folgende Funktionen:

- Verteilen der Information über Frequenzgenauigkeit und Synchronisation vom PHE an FME, OgK bzw. OSK (Organisations-Sprechkanal).

- Veranlassen der Senderabschaltung, wenn sich die Basisstation auf die Nachbarbasisstation aufsynchronisiert.

## 2 Schnittstellen

### 2.1 Externe Schnittstellen

#### 2.1.1 Schnittstelle zur Funkperipherie Funkdatensteuerung (FDS) und Prüf-/Bedienrechner (PBR)

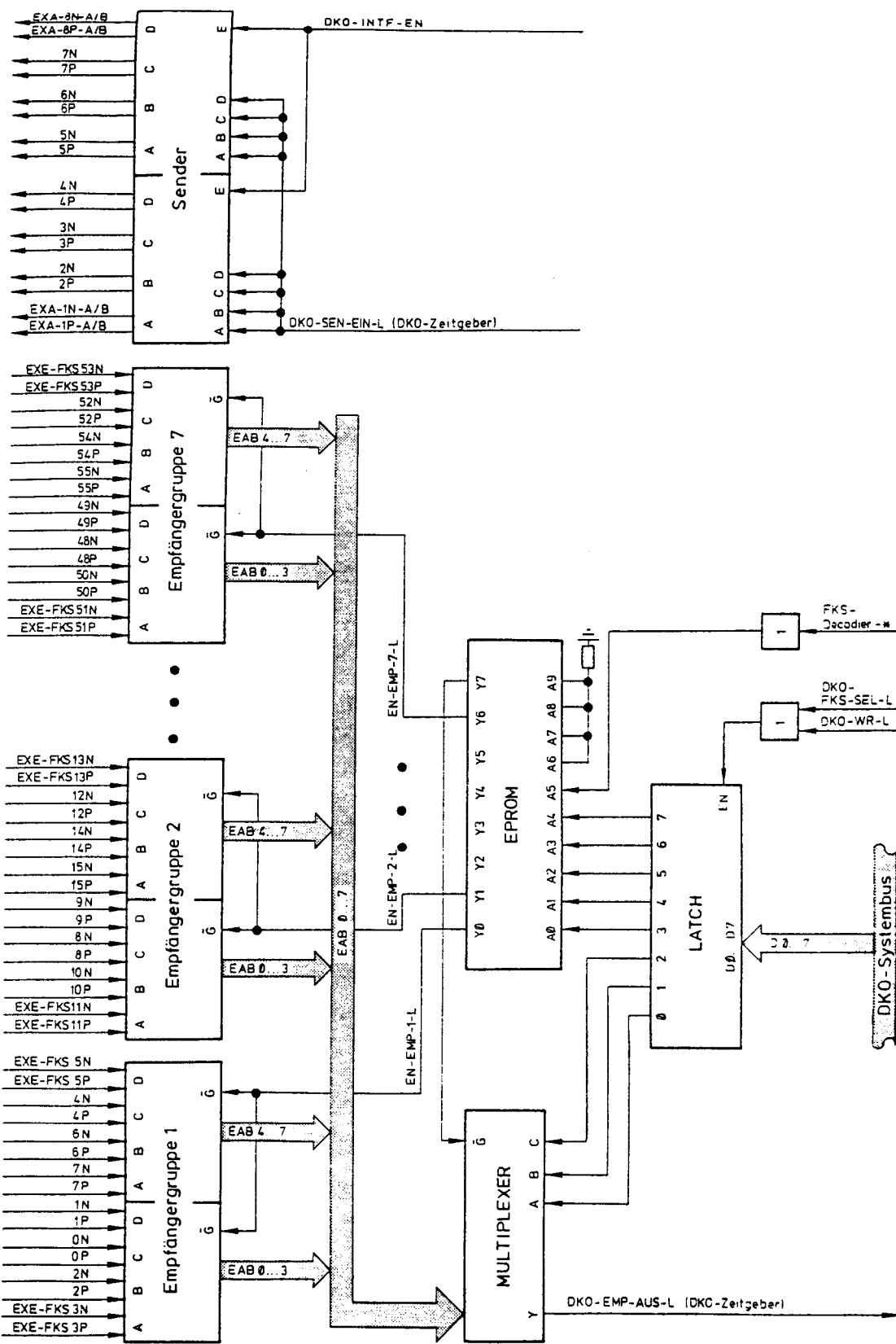

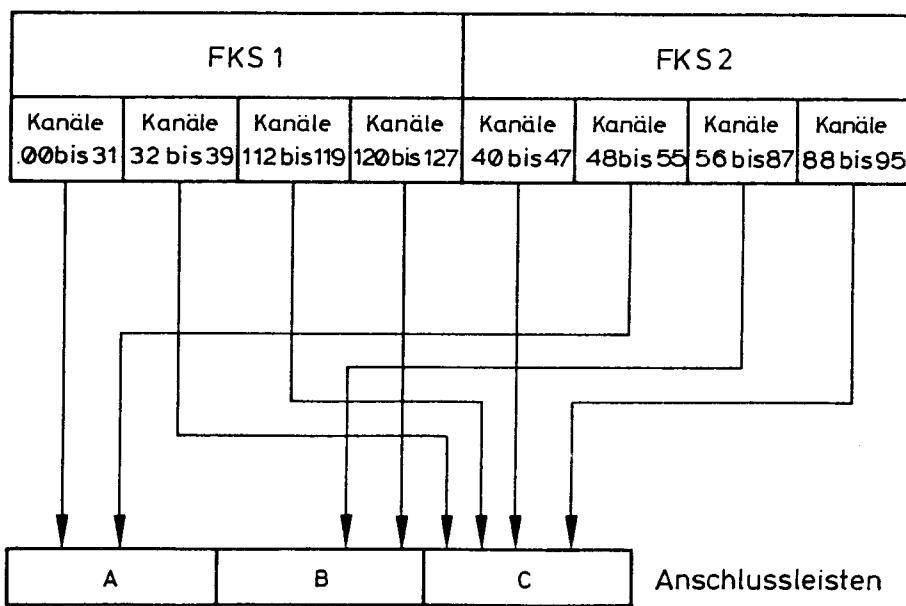

Die Schnittstelle FKS bedient maximal 112 Peripheriegeräte (SpK, OgK bzw. OSK, PHE, PFG, PBR und FME). Die Datenübertragung ist isochron, d. h. die Daten werden mit einem vom zentralen 6,4-MHz-Takt abgeleiteten Takt empfangen oder gesendet, das Datenformat ist jedoch asynchron. Die Daten bestehen aus einem Startbit, acht Datenbits und einem Stop-Bit. Die Umformung der Mikroprozessordaten in dieses Format und zurück wird vom EPCI-Baustein 2661 vorgenommen. Der Übertragungstakt beträgt 256 kHz.

Im folgenden wird für alle an die Schnittstelle angeschlossenen Einheiten die Abkürzung FKS benutzt.

Die Übertragung in Richtung FDS → FKS wird als Senden, die Übertragung in Richtung FKS → FDS als Empfang definiert.

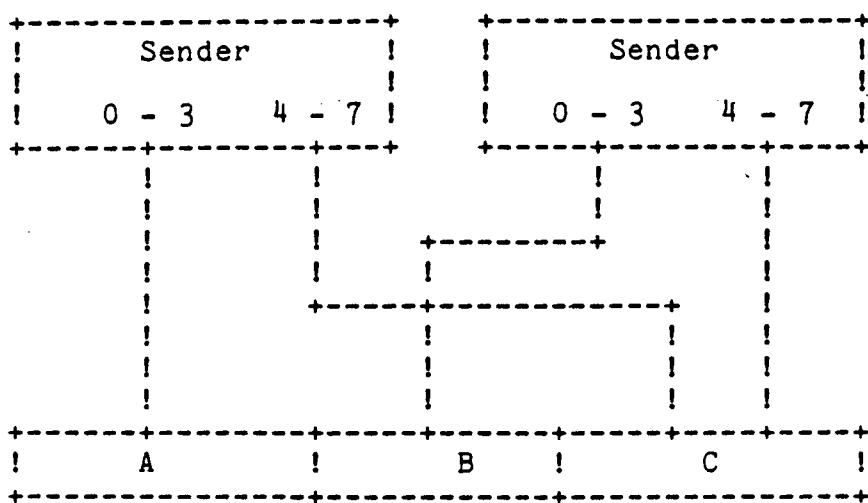

##### 2.1.1.1 Sendeschnittstelle

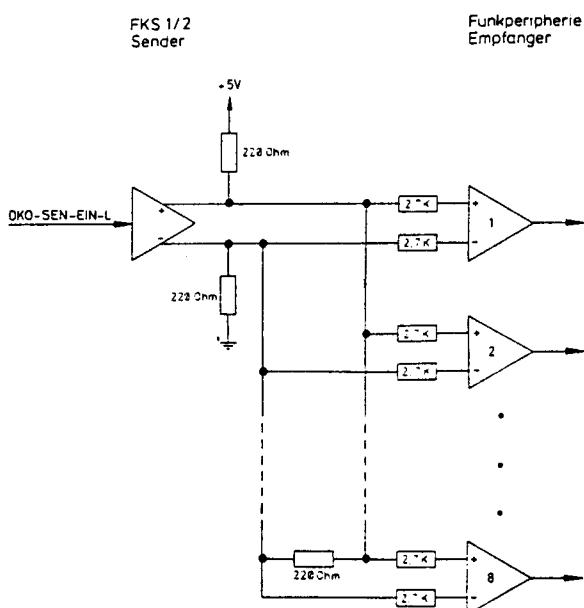

Die Sendeschnittstelle zu den FKS besteht aus 16 Sendern, die in vier symmetrischen Sendebausteinen enthalten sind. An jeden Sender können bis zu acht symmetrische Empfänger angeschlossen werden, die einen gemeinsamen Abschlußwiderstand und Serienschutzwiderstände haben. Der Sendetakt beträgt 256 kHz. Alle Sender senden gleichzeitig die gleichen Nachrichten zu den FKS.

Schnittstellensignale:

|               |                                                                                         |

|---------------|-----------------------------------------------------------------------------------------|

| EXA-iP-A      | positive Ader des Senders Nr. i der Schnittstellenplatte 1                              |

| EXA-iN-A      | negative Ader des Senders Nr. i der Schnittstellenplatte 1                              |

| EXA-iP-B      | positive Ader des Senders Nr. i der Schnittstellenplatte 2                              |

| EXA-iN-B      | negative Ader des Senders Nr. i der Schnittstellenplatte 2                              |

| DKO-SEN-EIN-L | Ausgang des EPCI 2661, Eingang der 16 symmetrischen Sender, serielle Daten mit 256 kHz. |

### **2.1.1.2 Empfangsschnittstelle**

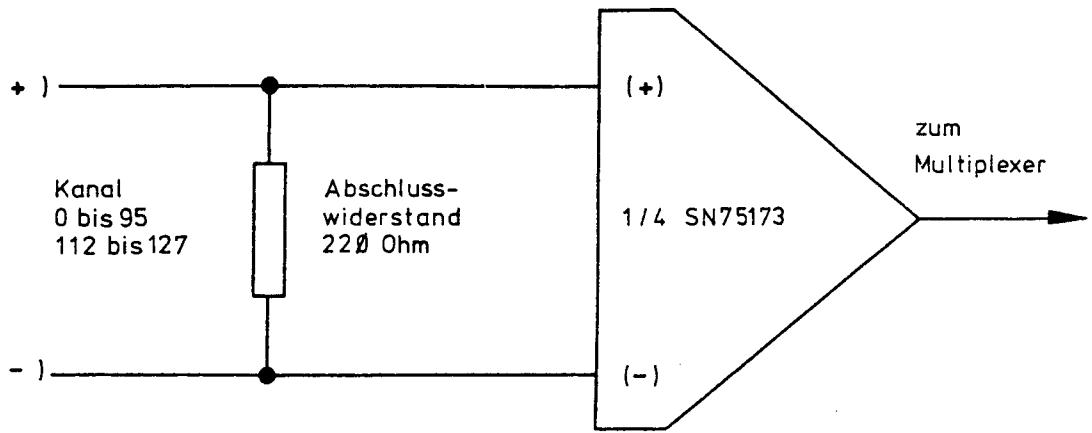

Die Empfangsschnittstelle besteht aus 112 symmetrischen Empfängern, d.h. aus 28 Bausteinen. Jedem Empfänger auf der Schnittstelle FKS entspricht ein FKS-Sender.

Die Beschaltung der Empfänger mit einem Abschluß- und Serienwiderstand dient der Sicherung des H-Pegels am Empfängerausgang, wenn die Senderausgänge hochohmig sind oder die Leitungen unterbrochen wurden.

Schnittstellensignale:

|                     |                                                       |

|---------------------|-------------------------------------------------------|

| <b>EXE-FKSxxP-A</b> | positive Ader Nr. xxH auf der Schnittstellenplatte 1  |

| <b>EXE-FKSxxN-A</b> | negative Ader Nr. xxH auf der Schnittstellenplatte 1  |

| <b>EXE-FKSxxP-B</b> | positive Ader Nr. xxH auf der Schnittstellenplatte 2  |

| <b>EXE-FKSxxN-B</b> | negative Ader Nr. xxH auf der Schnittstellenplatte 2. |

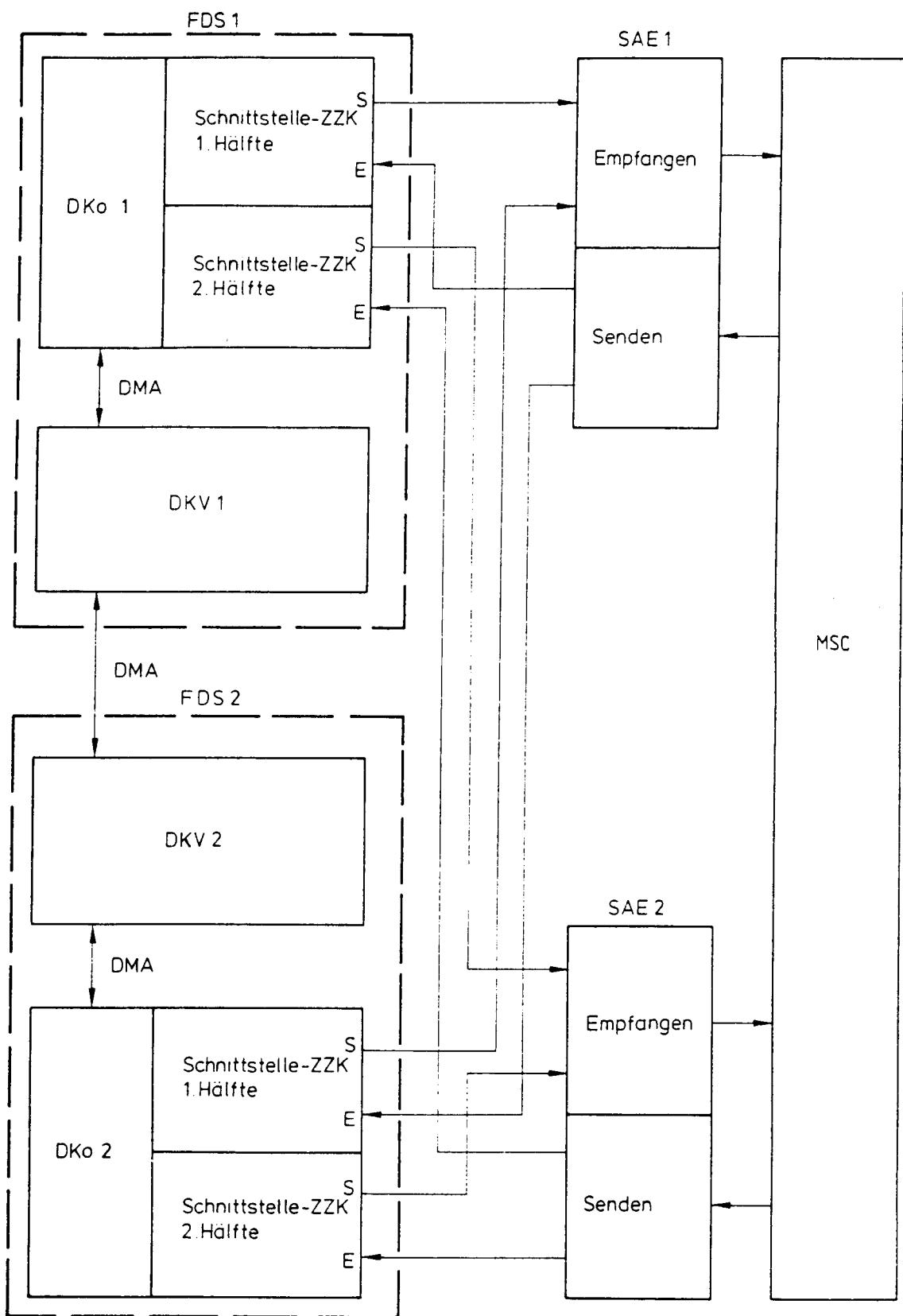

### **2.1.2 Schnittstelle zur Signalanpaßeinheit (SAE)**

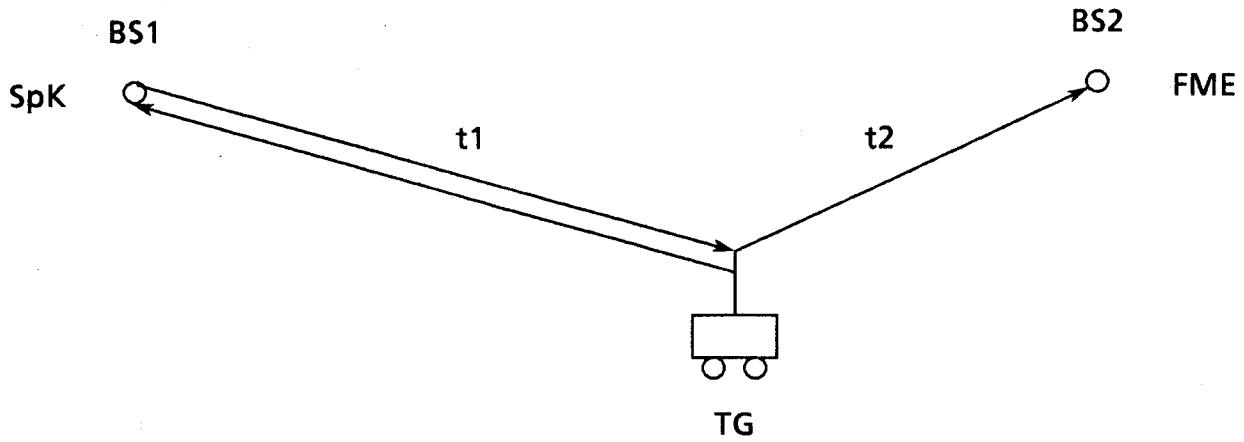

Sind beide SAE in Ordnung, wird über beide signalisiert. Damit im Störungsfall noch ein Betrieb mit halber Sendekapazität möglich ist, wird zwischen den beiden FDS und den SAE eine Datenverbindung aufgebaut; Bild 3 zeigt den grundsätzlichen Aufbau der Schnittstelle zur SAE.

Die SAE unterscheiden nicht zwischen FDS1 und FDS2:

- Die Empfangssignale sind über ein ODER-Gatter verknüpft

- Die Sendesignale sind gleich.

Die FDS können die SAE einzeln addressieren, wobei immer nur eine FDS aktiv ist.

Alle Signale auf der Schnittstelle zur SAE werden auf symmetrischen Leitungen übertragen. Bei Spannungsausfall auf der Sendeseite oder Auf trennung beider Adern, geht der Empfänger in High-Zustand.

Die Signalnamen haben folgende Form:

**EXz-Dz-zzzzzP-L** positive Ader bei allen Signalen ("z" für den Signalnamen)

**EXz-Dz-zzzzzN-L** negative Ader bei allen Signalen ("z" für den Signalnamen).

Bild 3 Schnittstelle zur Signalanpaßeinheit (SAE)

Das auf der positiven und negativen Ader liegende Signal wird nachfolgend als EXz-Dz-zzzzP/N-L bezeichnet.

Die Parameter x und y bezeichnen die entsprechende Gerätenummer:

x = SAE-Nummer

y = FDS-Nummer

Folgende Signale werden zwischen der FDS und der SAE ausgetauscht:

|                 |                                                                                                               |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| EXE-Dx-DSxSyP/N | Daten SAE → FDS, Quelle: SAE                                                                                  |

| EXE-Dx-CySxP/N  | Takt zur seriellen Übertragung der Daten                                                                      |

| EXE-Dx-RDySxP/N | SAE Lesesignal (SAE-RD) für Dateneinrichtung                                                                  |

|                 | SAE → FDS, Quelle: SAE                                                                                        |

| EXE-Dx-WRySxP/N | SAE Schreibsignal (SAE-WR) für Datenrichtung                                                                  |

|                 | FDS → SAE, Quelle: SAE                                                                                        |

| EXA-Dx-DFySxP/N | Daten FDS → SAE, Quelle: FDS                                                                                  |

| EXA-Dx-SBySxP/N | SEBER (sendebereit) aktiv: Die SAE darf einen Block aus dem FDS-Pufferspeicher lesen, Quelle: FDS             |

| EXA-Dx-EBySxP/N | EMBER (empfangsbereit) aktiv: Die SAE darf einen Block in den FDS-Pufferspeicher einschreiben.<br>Quelle: FDS |

### 2.1.3 Takschnittstelle zum Phasenempfänger (PHE)

Die Signale SET und T6,4MHz werden im PHE erzeugt. Das rechteckige Signal SET wird auf symmetrischen Leitungen und das sinusförmige Signal T6,4MHz auf einer Koaxialleitung übertragen, sie sind zueinander asynchron.

EXE-2,4S-P/N (SET), Periodendauer 2,4 s, Tastverhältnis 1:63.

Die zulässige Toleranz vom SET beträgt  $\pm 20 \mu\text{s}$ .

Das 6,4-MHz-Signal nach dem Empfänger ist ein Rechtektakt:

EXE-6,4MHz-P/N (T6,4M), Tastverhältnis 1:1.

### 2.1.4 Schnittstelle zur Parallel-FDS

Die Schnittstelle zur Parallel-FDS besteht aus 28 bidirektionalen und 16 unidirektionalen Leitungen.

#### **2.1.4.1 Bidirektionale Leitungen**

- 8 Datenleitungen EXB-D0...7

- 16 Adreßleitungen EXB-A0...15

- 4 Steuerleitungen EXB-DIR, EXB-ADE-L, EXB-MEN-L, EXB-RD-L

Die 5. Steuerleitung (DKV-WR-L) ist nicht mit der DKV2 verbunden, damit die DKV nur im eigenen RAM schreiben und die Daten der Nachbar-DKV nicht verändern kann (defekte FDS kann in aktiver keine Fehler verursachen).

Die Daten-, Adreß- und Steuerleitungen sind zur Parallel-DKV mit Treibern versehen.

#### **2.1.4.2 Unidirektionale Leitungen**

Eingangsleitungen:

|                            |                   |

|----------------------------|-------------------|

| 4 Leitungen Interrupttyp   | EXE-TYP0 bis TYP3 |

| 1 Interruptleitung         | EXE-INTDKV2-L     |

| 1 Quittungsleitung         | EXE-QUIDKV2-L     |

| 1 HOLD-Request-Leitung     | EXE-DKV-HRQ-L     |

| 1 HOLD-Acknowledge-Leitung | EXE-DKV-HAC-L     |

Ausgangsleitungen:

|                            |                   |

|----------------------------|-------------------|

| 4 Leitungen Interrupttyp   | EXA-TYP0 bis TYP3 |

| 1 Interruptleitung         | EXA-INTDKV2-L     |

| 1 Quittungsleitung         | EXA-QUIDKV2-L     |

| 1 HOLD-Request-Leitung     | EXA-DKV-HRQ-L     |

| 1 HOLD-Acknowledge-Leitung | EXA-DKV-HAC-L     |

Über die Interruptleitung wird in der DKV2 ein Interrupt erzeugt. Daraufhin liest die DKV2 über die vier Interrupttyp-Leitungen den Interrupttyp ein und kann darauf reagieren. Um mitzuteilen, daß sie mit den von ihr geforderten Tätigkeiten fertig ist, wird von ihr die Quittungsleitung aktiviert.

Die HOLD-Request- und HOLD-Acknowledge-Leitungen werden für den DMA benötigt.

Alle Signale zwischen den DKV-Prozessorbaugruppen laufen über Treiber, die jeweils von einem Sperrsignal (DKV-DKV2-INH-H) aus der eigenen Sicherheitsbaugruppe gesperrt werden, wenn

- bei der FDS2 die Spannung ausgefallen ist oder

- die eigene FDS in Fehlerbehandlung und/oder defekt ist.

Damit wird verhindert, daß bei einem Fehler im Netzteil der FDS2, der eine Schwankung der Ausgangsspannung zwischen 0 V und 5 V zur Folge hat, falsche Interruptanforderungen den Rechnerbetrieb in den intakten FDS stören. Ferner wird dadurch verhindert, daß die Treiber in beiden FDS durch unkontrolliertes Verhalten der fehlerhaften FDS gegeneinander arbeiten können.

## 2.1.5 Sicherheitstechnische Schnittstellen

### 2.1.5.1 Schnittstellen zu den Netzteilen

Die Störungssignalisierungen sollen von der FDS über den PBR zum Regionalen Wartungszentrum (RWZ) übertragen werden. Die Störungssignalisierungen der Netzteile werden unmittelbar von der FDS-Sicherheitstechnik in jeder FDS erfaßt. Diese setzt eine Störungsmeldung zum RWZ ab.

Die in der Tabelle 1 dargestellten Systemkomponenten werden über ein eigenes Netzteil versorgt und von einer eigenen Leitung überwacht.

Folgende Abkürzungen werden in Bild 4 und in den Tabellen 1 und 2 verwendet:

|     |                                   |

|-----|-----------------------------------|

| AKT | aktiv                             |

| BLD | Batterieladen                     |

| BZ  | Betriebszustand                   |

| DEF | defekt                            |

| FEB | Fehlerbehandlung                  |

| FI  | Fehler-Interrupt                  |

| FV  | Frequenzverteiler (Taktverteiler) |

| HW  | Hardware                          |

| PAS | passiv                            |

| ST  | Sicherheitstechnik                |

| VEF | verfügbar                         |

| ZG  | Zentralgestell                    |

Ein Netzteilausfall wird über symmetrische Leitung auf der Sicherheitstechnik erfaßt und über Fehlerinterrupt der DKV signalisiert.

**Tabelle 1 Schnittstellensignale zu den Netzteilen**

| Signalname<br>an der FDS | Quelle                                                       | Ziel                | Bedeutung                                               |

|--------------------------|--------------------------------------------------------------|---------------------|---------------------------------------------------------|

| EXE-FKM-AUSF-P/N         | Netzteil im FKS-Gestell<br>(OgK, SpK)                        | ST-HW,<br>beide FDS | Spannungsstörung<br>im FKS-Gestell                      |

| EXE-FME-AUSF-P/N         | Netzteil im FME-Gestell                                      | ST-HW,<br>beide FDS | Spannungsstörung<br>im FME-Gestell                      |

| EXE-ANT-AUSF-P/N         | Reserve                                                      | ST-HW,<br>beide FDS |                                                         |

| EXE-5V-AUSF-L            | Netzteil im eigenen<br>Zentralgestell,<br>FDS-5V-Überwachung | ST-HW,<br>FDS1      | 5-V-Ausfall im eige-<br>nen Netzteil (Power<br>On, POR) |

| EXE-60V-AUSF-L           | Netzteil im eigenen ZG                                       | ST-HW,<br>FDS1      | Primärspannungs-<br>störung/ZG                          |

| EXE-BLD-AUSF-L           | Netzanlage<br>(Batterieladung)                               | ST-HW,<br>beide FDS | Batterieladung-<br>Ausfall/Wiederkehr                   |

| EXE-FDS2-AUS-FP/N        | Netzteil im anderen ZG                                       | DKV/<br>eigenes ZG  | Spannungsstörung<br>FDS oder PHE, FV,<br>PFG            |

| EXE-5V-DKV2-L            | ST-HW, FDS2                                                  | ST-HW,<br>FDS1      | 5V/FDS-Störung im<br>anderen ZG                         |

### 2.1.5.2 Schnittstelle zur FDS2

Tabelle 2 Schnittstellensignale zur FDS2

| Signalname   | Quelle      | Ziel        | Bedeutung                                                      |

|--------------|-------------|-------------|----------------------------------------------------------------|

| EXE-ST-AKT-L | ST-HW,FDS2  | ST-HW, FDS1 | Signalisierung des aktiven Zustandes der FDS2 an FDS1          |

| EXE-ST-VEF-L | ST-HW, FDS2 | ST-HW, FDS1 | Signalisierung der Verfügbarkeit der FDS2 an FDS1              |

| EXE-ST-FEB-H | ST-HW, FDS2 | ST-HW, FDS1 | Signalisierung des Fehlerbehandlungszustandes der FDS2         |

| EXE-ST-DEF-H | ST-HW, FDS2 | ST-HW, FDS1 | Signalisierung des defekten Zustandes der FDS2 an FDS1         |

| EXE-ST-INT-H | ST-HW, FDS2 | ST-HW, FDS1 | Interrupt der FDS2 an FDS1                                     |

| EXA-ST-AKT-L | ST-HW, FDS1 | ST-HW, FDS2 | Signalisierung des aktiven Zustandes der FDS1 an FDS2          |

| EXA-ST-VEF-L | ST-HW, FDS1 | ST-HW, FDS2 | Signalisierung der Verfügbarkeit der FDS1 an FDS2              |

| EXA-ST-FEB-H | ST-HW, FDS1 | ST-HW, FDS2 | Signalisierung des Fehlerbehandlungszustandes der FDS1 an FDS2 |

| EXA-ST-DEF-H | ST-HW, FDS1 | ST-HW, FDS2 | Signalisierung des defekten Zustandes der FDS1 an FDS2         |

| EXA-ST-INT-L | ST-HW, FDS1 | ST-HW, FDS2 | Interrupt der FDS1 an FDS2                                     |

### 2.1.5.3 Schnittstelle Netzteil - Baugruppe Aktivdatei

Die Baugruppe Aktivdatei enthält die Teilnehmerliste und die Betriebsdaten für die Basisstation (Anlagenliste). Die Anlagenliste wird entweder batteriegepuffert oder über MSC gesetzt. Sie besteht aus RAM - oder aus batteriegepufferten NV-RAM-Bausteinen. Der Netzteil liefert bei Unterschreiten der Sekundärspannung 5 V um 4% bis 7% das Spannungsausfallssignal EXE-5V-AUSF-L. Das Chip-Select des Rechners für die Anlagenliste wird mit diesem Signal verknüpft und bei Spannungsunterschreitung gesperrt. Ab 4,4 V schaltet ein eventuell eingebauter NV-RAM auf interne Batterieversorgung um und sperrt gleichzeitig alle Ein- und Ausgänge.

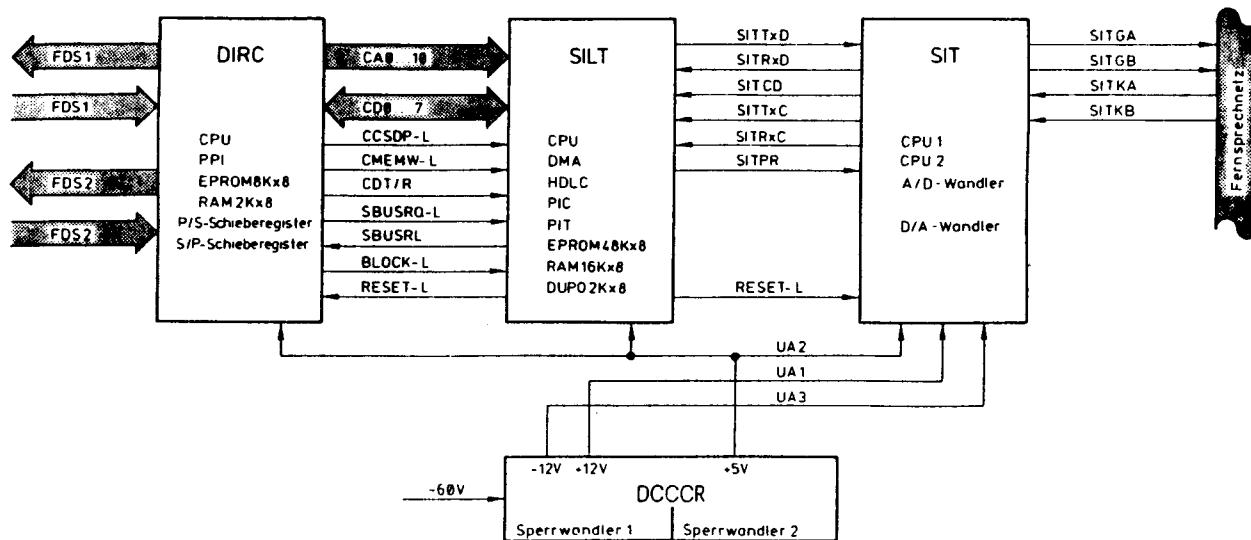

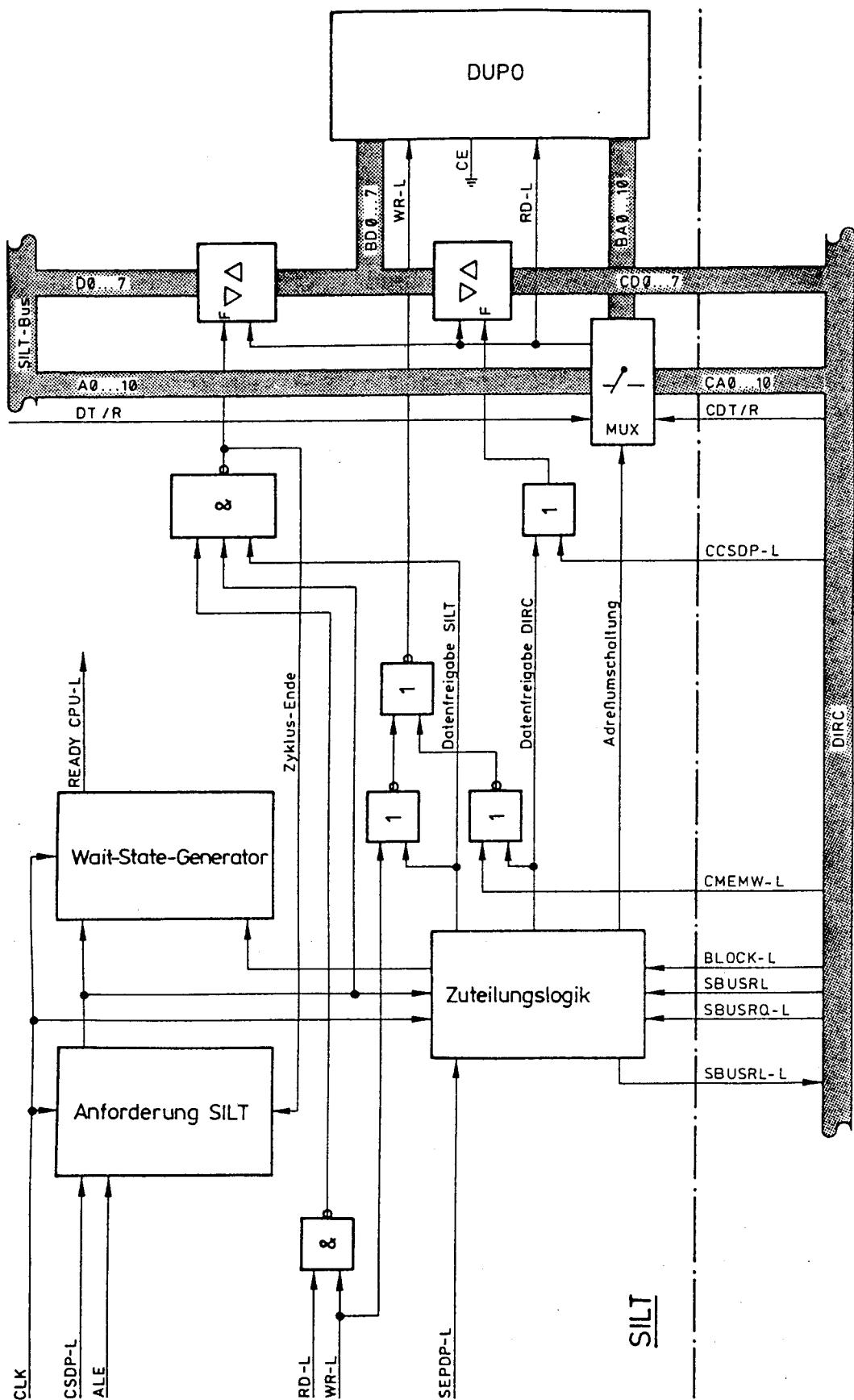

## 2.2 Interne Schnittstellen

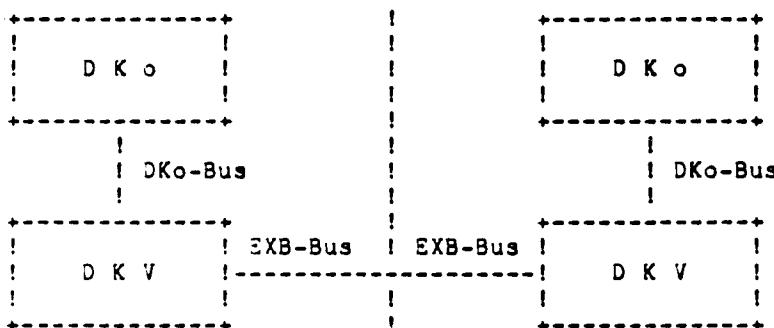

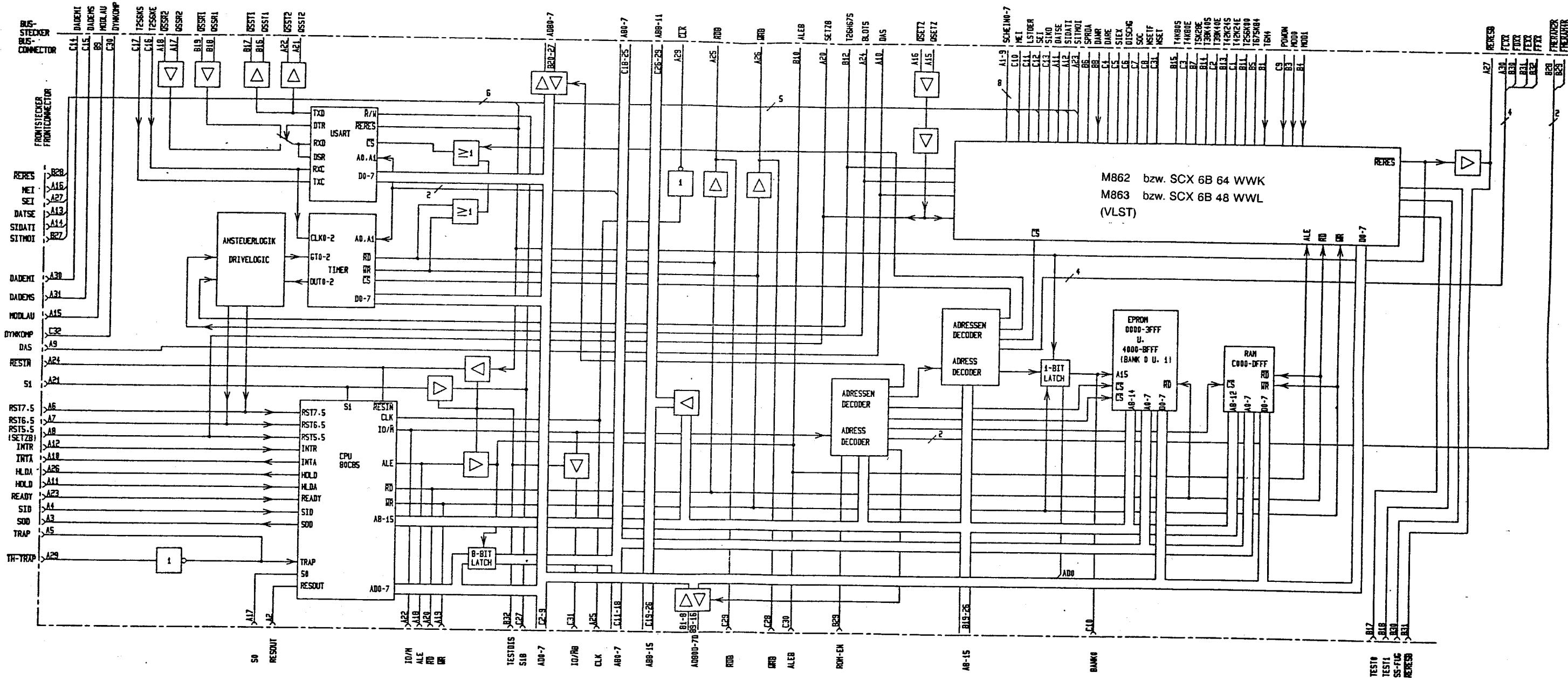

### 2.2.1 FDS-Bussystem

In der FDS wird ein einheitliches Bussystem verwendet. Es besteht aus einem 16-bit Adreßbus, 8-bit-Datenbus und 5-bit-Steuerbus. Die Signale sind einheitlich bezeichnet und tragen als Präfix den Namen des Rechners (DKo oder DKV), bzw. EXB für den Bus zwischen den beiden DKV

- Adreßbus: A0...15

- Datenbus: D0...7

- Steuerbus: DIR      Datenrichtung

MEN-L    Speicherfreigabe

RD-L     Lesesignal

WR-L     Schreibsignal

ADE-L    Adreßfreigabe

Die Adreß- und Steuerbussignale werden vom jeweiligen Busmaster (CPU, DMA-Steuerung, oder Nachbar-FDS) erzeugt.

Die Rechnerbusse sind folgendermaßen verbunden:

Bild 4 FDS-Bussystem

Daten zwischen den Rechnern werden nur über DMA übertragen und durch die DKV gesteuert.

In diesem Bussystem sind folgende DMA-Transferarten möglich:

- DMA DKV intern

- DMA DKo – DKV

- DMA DKV – DKV

#### 2.2.1.1 Adreß- und Datenbus

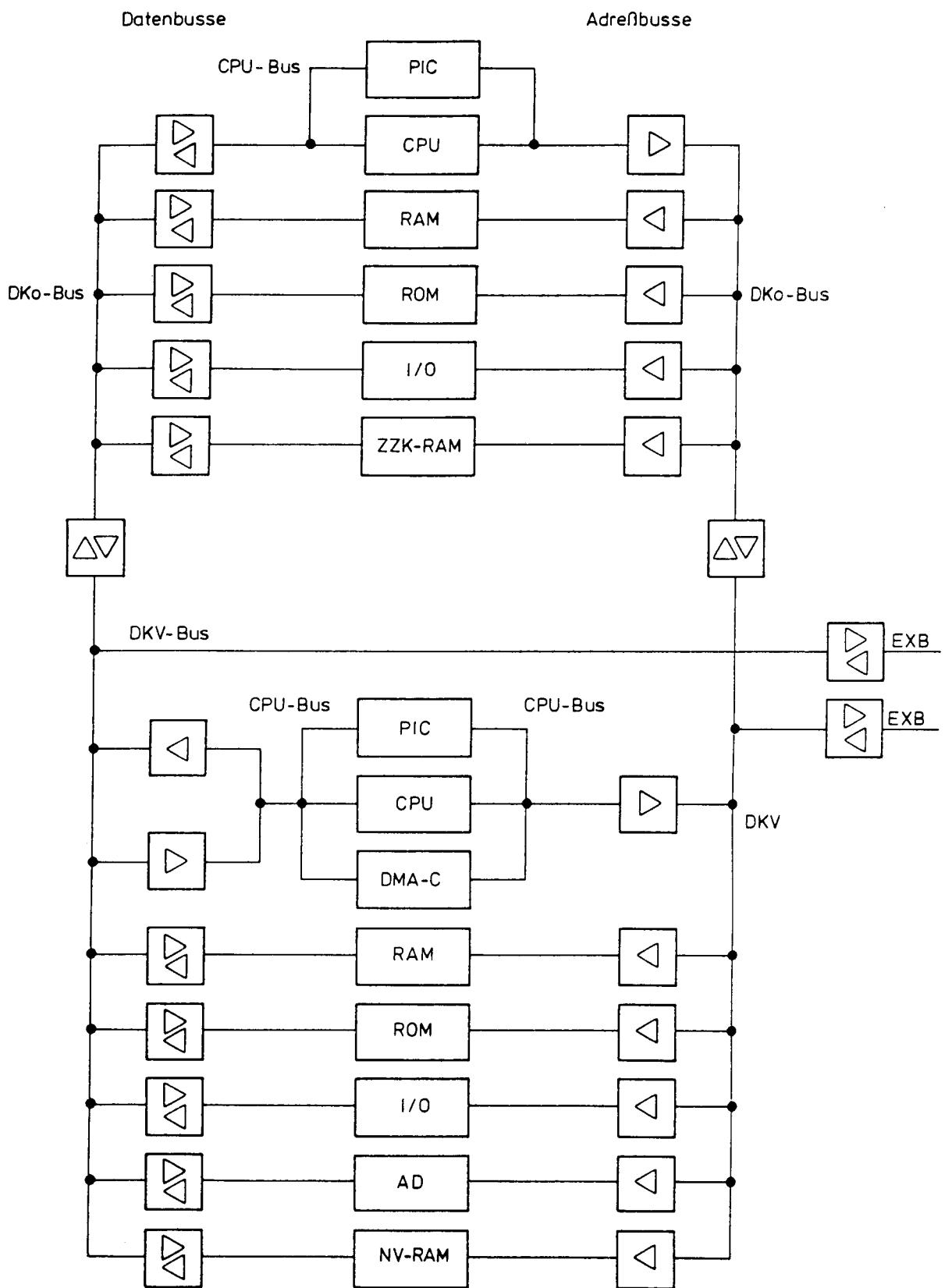

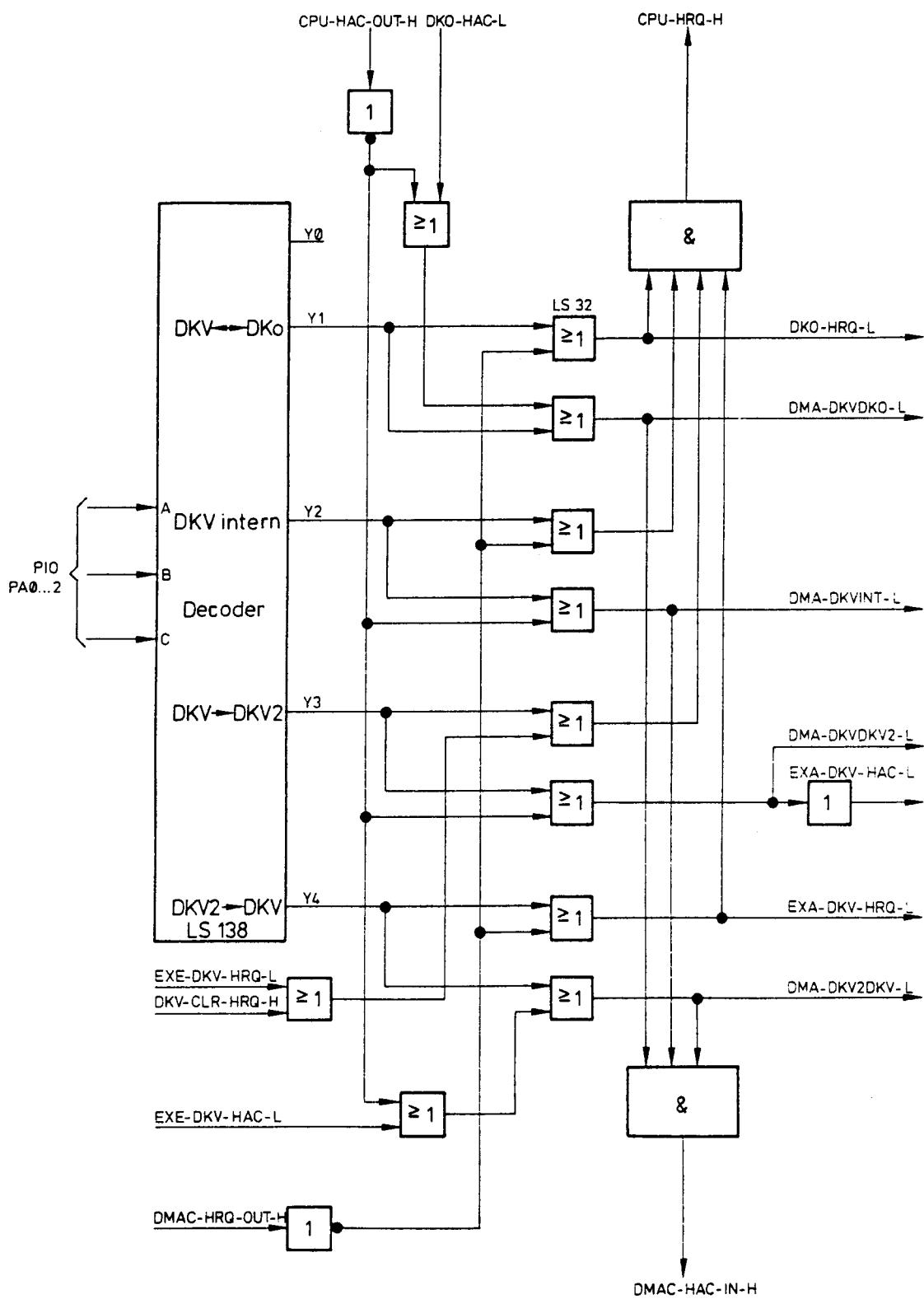

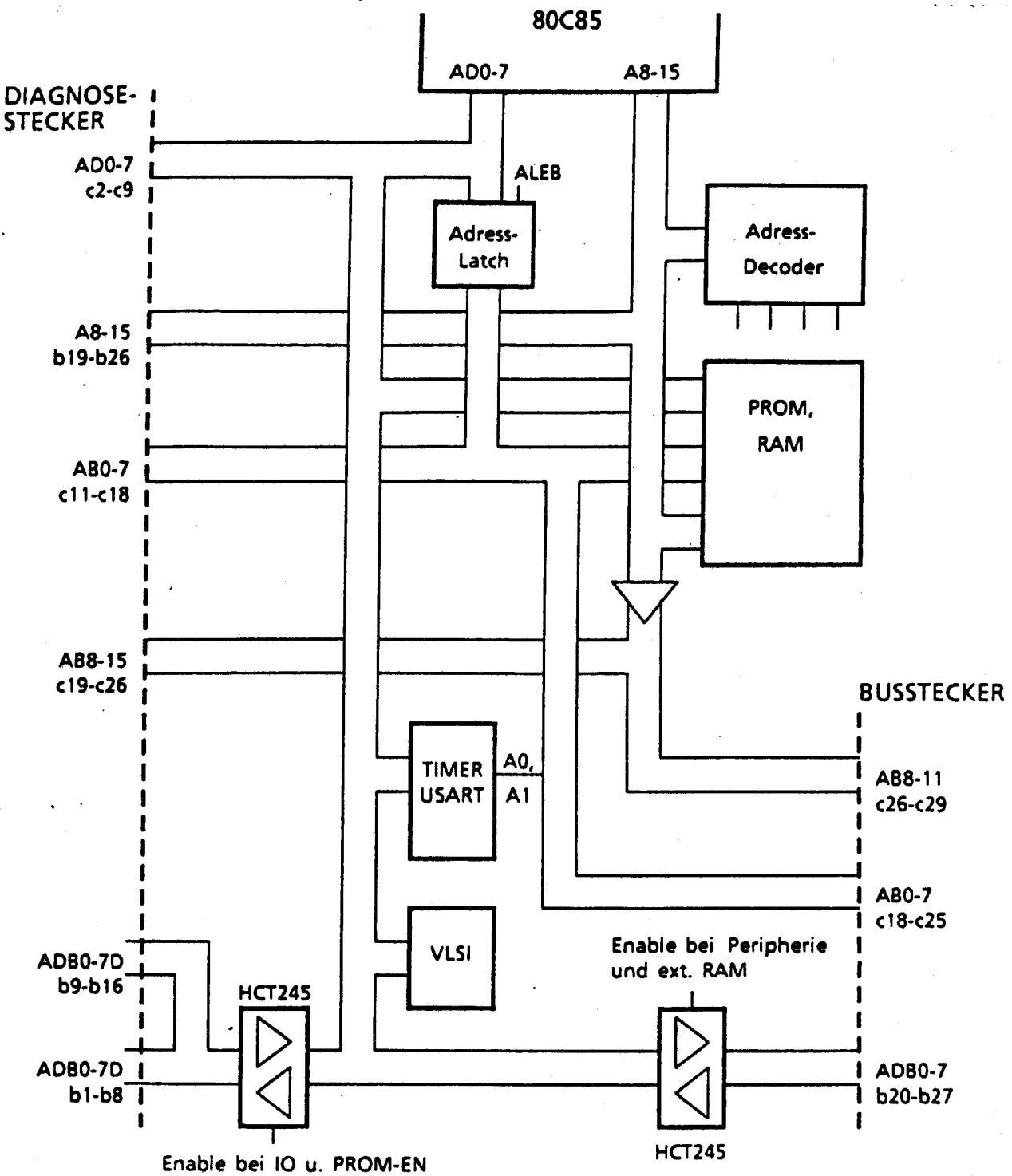

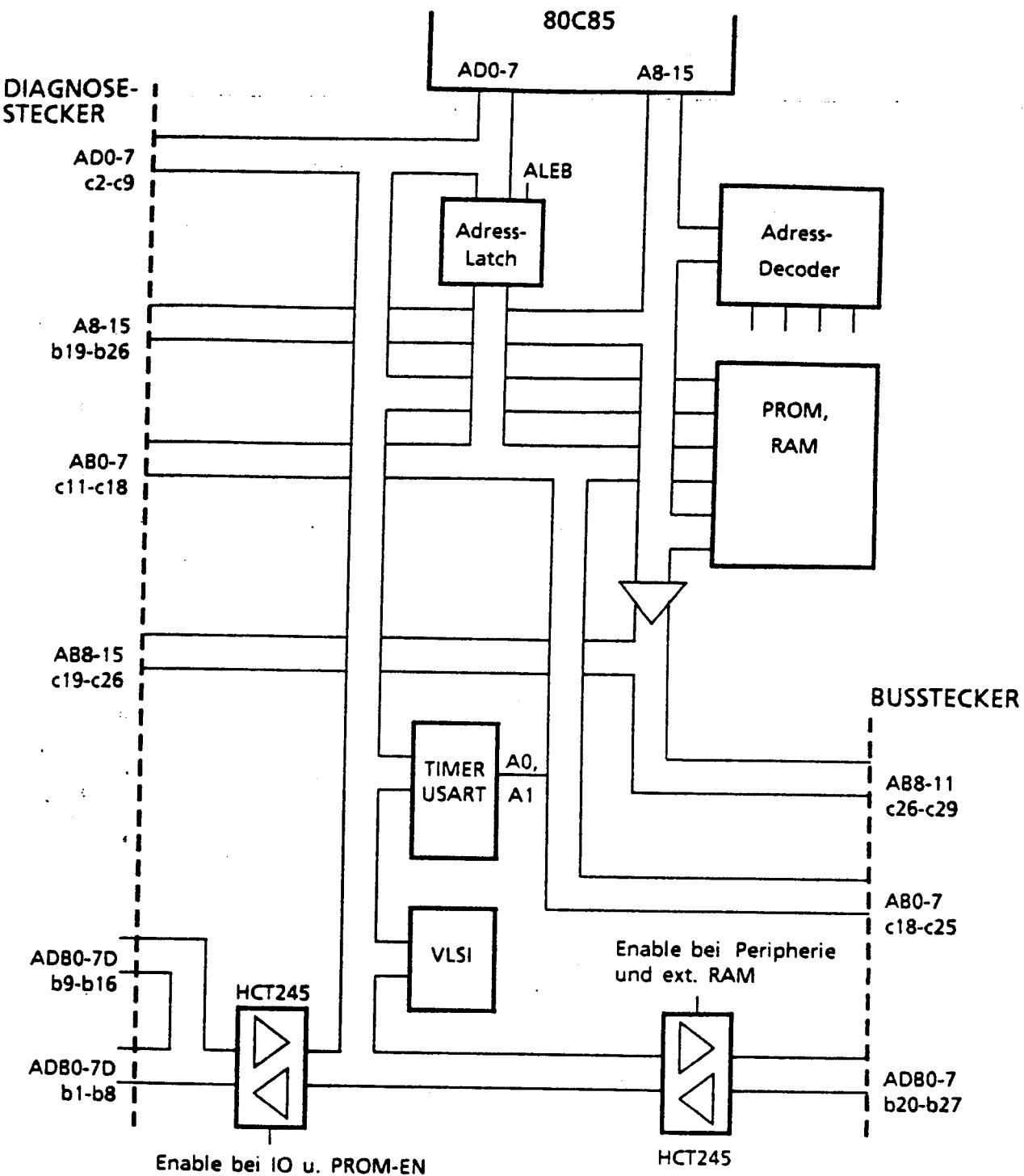

Im Bild 5 ist der Aufbau der Adreß- und Datenbusse innerhalb einer FDS dargestellt.

Bild 5 Adreß- und Datenbus

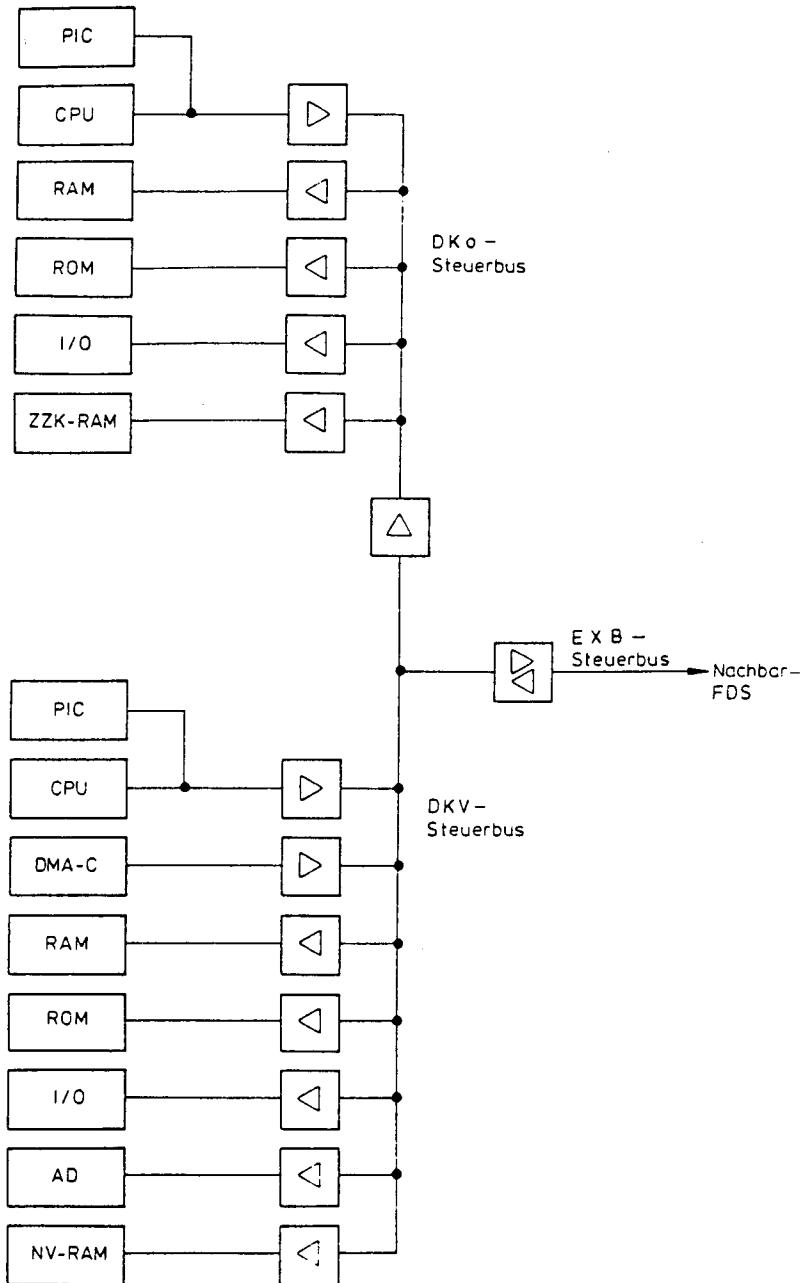

### 2.2.1.2 Steuerbus

Der DKV (DKo)-Steuerbus besteht aus folgenden Signalen:

- |                 |                                                  |

|-----------------|--------------------------------------------------|

| DKV (DKo)-DIR   | Datenrichtung                                    |

| DKV (DKo)-MEN-L | Speicherfreigabe                                 |

| DKV (DKo)-RD-L  | Lesesignal                                       |

| DKV (DKo)-WR-L  | Schreibsignal (im EXB-Steuerbus nicht enthalten) |

| DKV (DKo)-ADE-L | Adreßfreigabe.                                   |

Bild 6 Steuerbus

## 2.2.2 Taktschnittstelle

Folgende Taktsignale werden innerhalb der FDS benötigt:

|               |                                                                                                                                                                                                                                                                                                      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DKO-SETBLZ-L  | Ein Impuls mit der Länge von 10 Taktperioden des 6,4-MHz-Taktes ( $1,56 \mu s$ ), der den Blockzähler bei jedem Rahmenbeginn (alle 2,4 s) in der DKo und DVK mit dem Wert 64D lädt. Er ist vom zentralen Signal SET des PHE abgeleitet und wird in Zusammenhang mit SET oder Power-On-Reset erzeugt. |

| DKO-T256K-L   | Ein Takt mit der Frequenz von 256 kHz, abgeleitet vom zentralen 6,4-MHz-Takt, geführt auf den Takteingang der Zeitgeber 8254 im DKo und DVK.                                                                                                                                                         |

| INT-T37,5MS-L | Takt für den Blockzähler von DKo und DVK zum Setzen der Zeitgeber-Zähler auf den Anfangswert.                                                                                                                                                                                                        |

| DVK-CLK       | Takt (3,072 MHz) für CPU und DMA Steuerung. Dient in der Aktivdatei als Arbeitstakt und in der DVK-Sicherheitstechnik zum Überwachen des 6,4-MHz-Taktes.                                                                                                                                             |

| DKO-T6,4M     | Zentraler Basisstation-Takt 6,4 MHz vom DKo-Zeitgeber an die DVK-Sicherheitstechnik. Er wird auf der DVK-Sicherheits-Baugruppe mit dem DVK-CLK überwacht.                                                                                                                                            |

| DKO-SET       | Ein bei der Rückflanke von SET abgeleitetes Signal des DKo-Zeitgebers an die DVK-Sicherheitstechnik, dient zum Überwachen der Teilerkette des DKo-Zeitgebers.                                                                                                                                        |

| DKO-UBWT-H    | Wird im DKo-Zeitgeber gebildet und dient in der DVK-Sicherheitstechnik zum Überwachen des SET-Signals.                                                                                                                                                                                               |

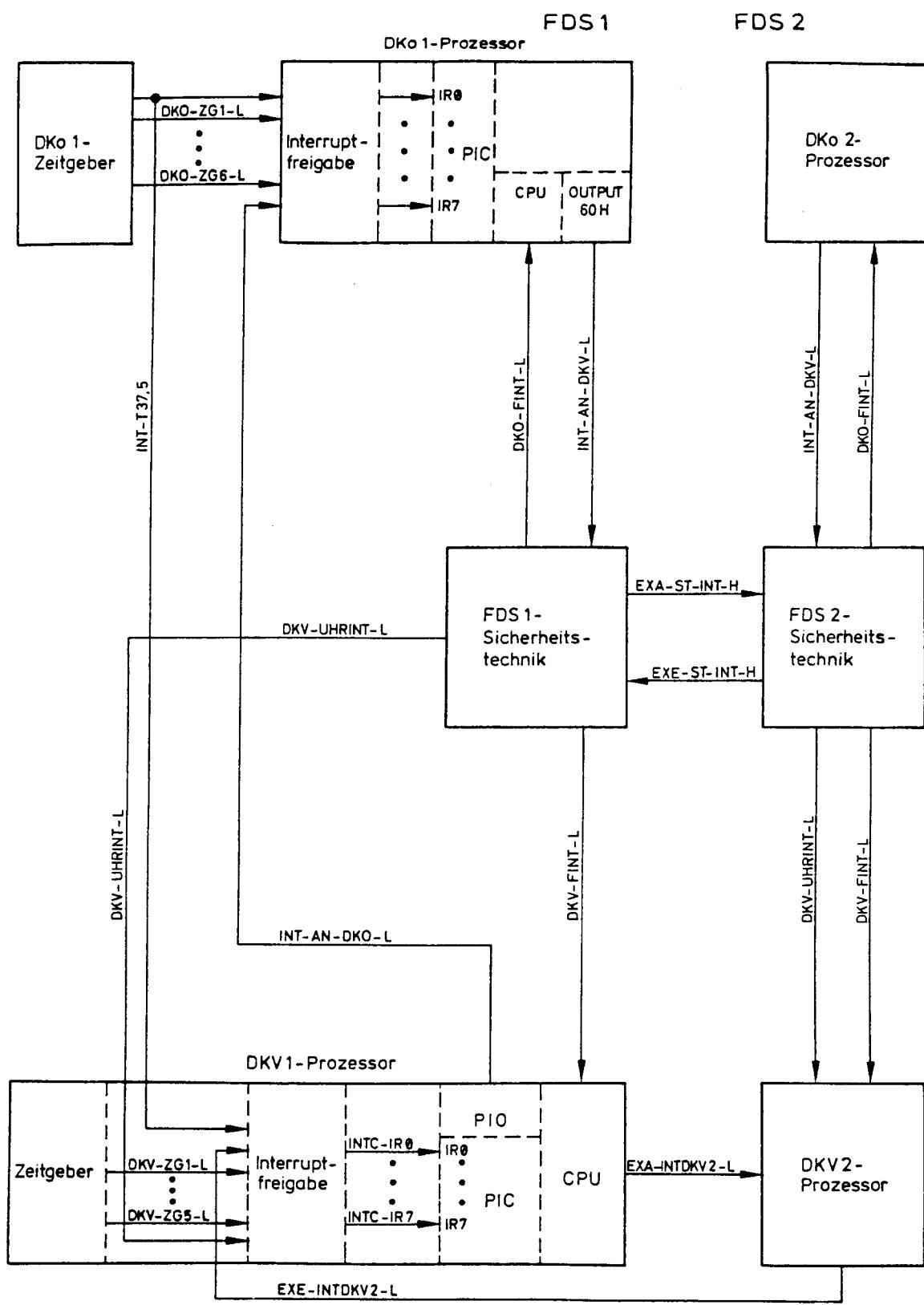

## 2.2.3 Interrupt-Signale

Die Interrupt-Eingänge der Unterbrechungssteuerung in DKo und DVK werden mit der Anstiegsflanke der Interrupt-Signale angesteuert. Die nachfolgend beschriebenen Interrupt-Signale sind im Bild 7 dargestellt.

|             |                                                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT-T37,5MS | Block-Interrupt des DKo-Zeitgebers an IRO der DKo- und DVK-Unterbrechungssteuerung. Die Impulsdauer entspricht einer Taktperiode des 256-kHz-Taktes. |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

Bild 7 Interrupt-Signale der Funkdatensteuerung

|                     |                                                                                                                                                                                                                                                                               |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>INT-AN-DKO-L</b> | Interrupt von DKV an IR7 des DKo.<br>Wird zur DMA-Übertragung zwischen DKV und DKo verwendet. Wird auf der DKo-Prozessor-Baugruppe negiert und auf die Unterbrechungssteuerung geführt, damit er mit der Vorderflanke erkannt wird.                                           |

| <b>DKV-FINT-L</b>   | Fehler-Interrupt von der FDS-Sicherheitstechnik an den DKV-Prozessor. Wird auf der DKV-Prozessor-Baugruppe negiert und an Eingang RST 7,5 der CPU geführt.                                                                                                                    |

| <b>DKO-FINT-L</b>   | Fehler-Interrupt von der FDS-Sicherheitstechnik an den DKo-Prozessor. Wird auf der DKV-Prozessor-Baugruppe negiert und an den Eingang RST 7,5 der CPU geführt.                                                                                                                |

| <b>DKV-UHRINT-L</b> | Uhr-Interrupt des Uhrenbausteins der Sicherheitstechnik an IR7 der DKV-Prozessor-Unterbrechungseinheit.<br>Wird auf der DKV-Prozessor-Baugruppe negiert, damit er mit der Vorderflanke erkannt wird. Dieses Signal wird erst inaktiv, wenn der Uhrenbaustein ausgelesen wird. |

| <b>INT-AN-DKV-L</b> | Fehler-Interrupt vom DKo-Ausgabebaustein (Adresse 60H, Bit 2), geführt über die Sicherheitstechnik-Baugruppe an Eingang RST 7,5 der DKV-CPU (Signal DKV-FINT-L). Der DKV-Prozessor erkennt die Vorderflanke.                                                                  |

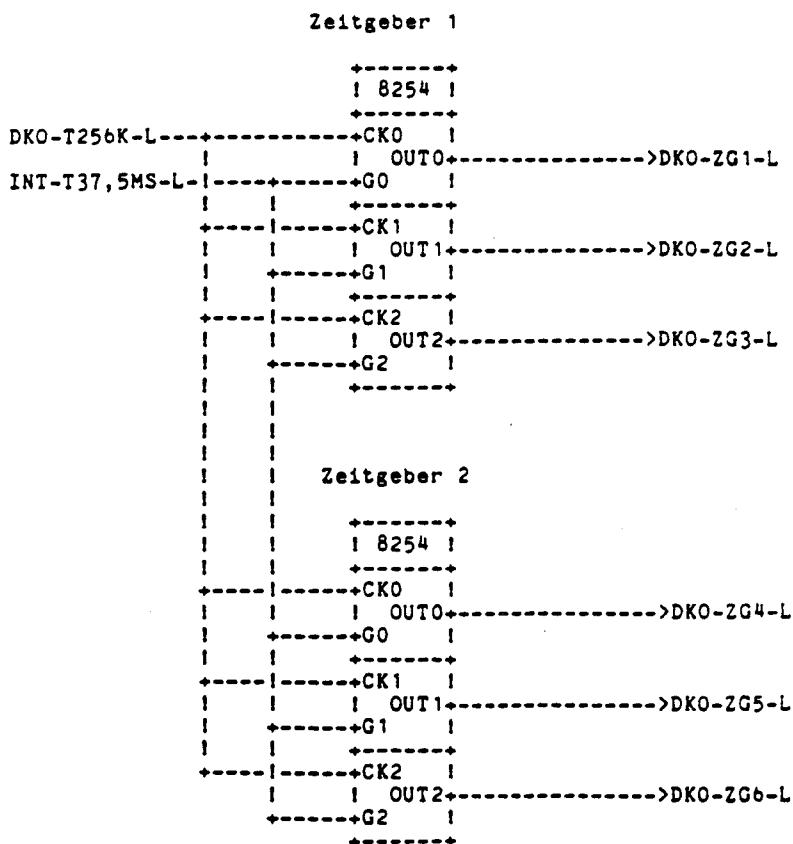

Folgende Zeitgeber-Interrupt-Signale werden beim Ablauf der DKV- und DKo-Zähler erzeugt:

- Interrupt-Signale des DKo-Zeitgebers

|                     |                      |

|---------------------|----------------------|

| <b>Zeitgeber 1:</b> | Zähler 0 erzeugt IR1 |

|                     | Zähler 1 erzeugt IR2 |

|                     | Zähler 2 erzeugt IR3 |

- Zeitgeber 2:

|                      |

|----------------------|

| Zähler 0 erzeugt IR4 |

| Zähler 1 erzeugt IR5 |

| Zähler 2 erzeugt IR6 |

- Interrupt-Signale des DKV-Zeitgebers

|                     |                      |

|---------------------|----------------------|

| <b>Zeitgeber 1:</b> | Zähler 0 erzeugt IR2 |

|                     | Zähler 1 erzeugt IR3 |

|                     | Zähler 2 erzeugt IR4 |

|                     |                      |

|---------------------|----------------------|

| <b>Zeitgeber 2:</b> | Zähler 0 erzeugt IR5 |

|                     | Zähler 1 erzeugt IR6 |

#### **2.2.4 Sicherheitstechnische Schnittstellen**

**Alle Angaben der sicherheitstechnischen Schnittstellen sind unter Pkt. 3.3 beschrieben und in Bild 32 dargestellt.**

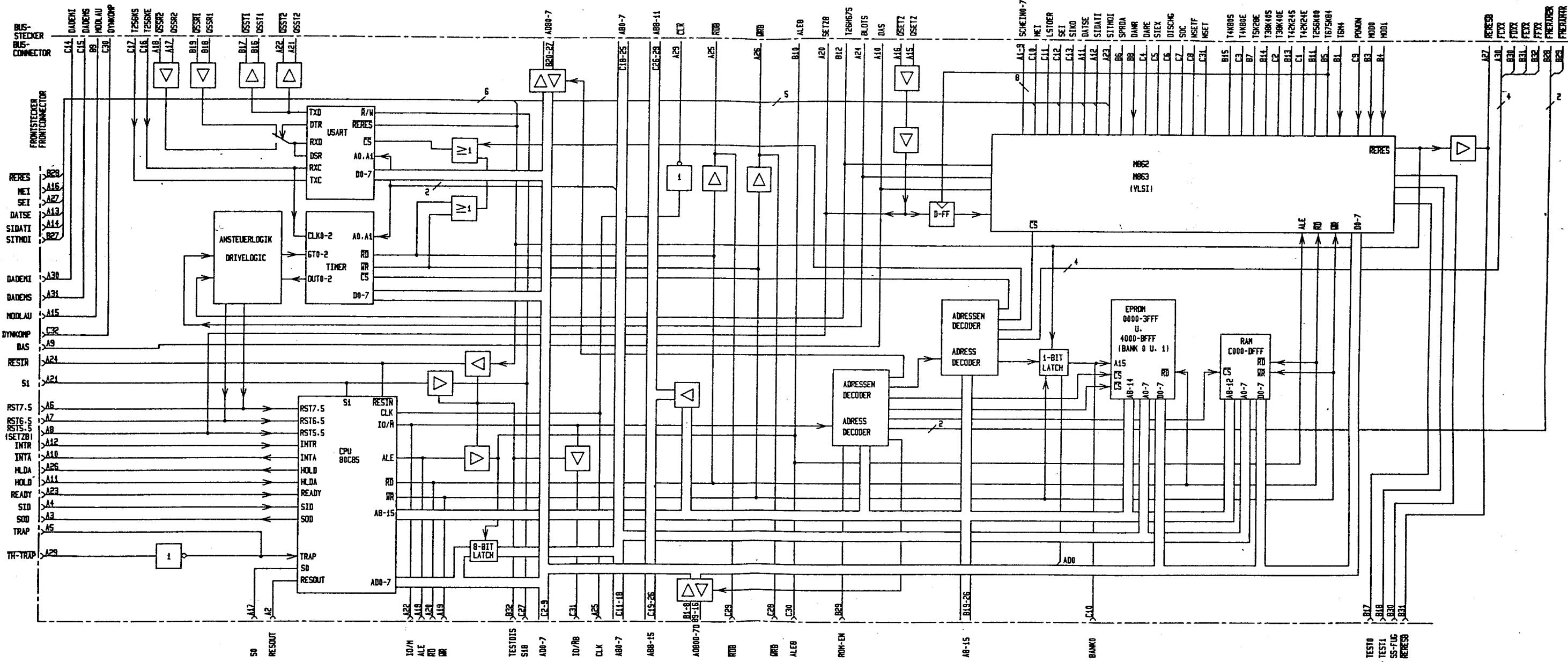

### **3 Funkdatensteuerung (FDS)**

#### **3.1 Datenkonzentrator DKo**

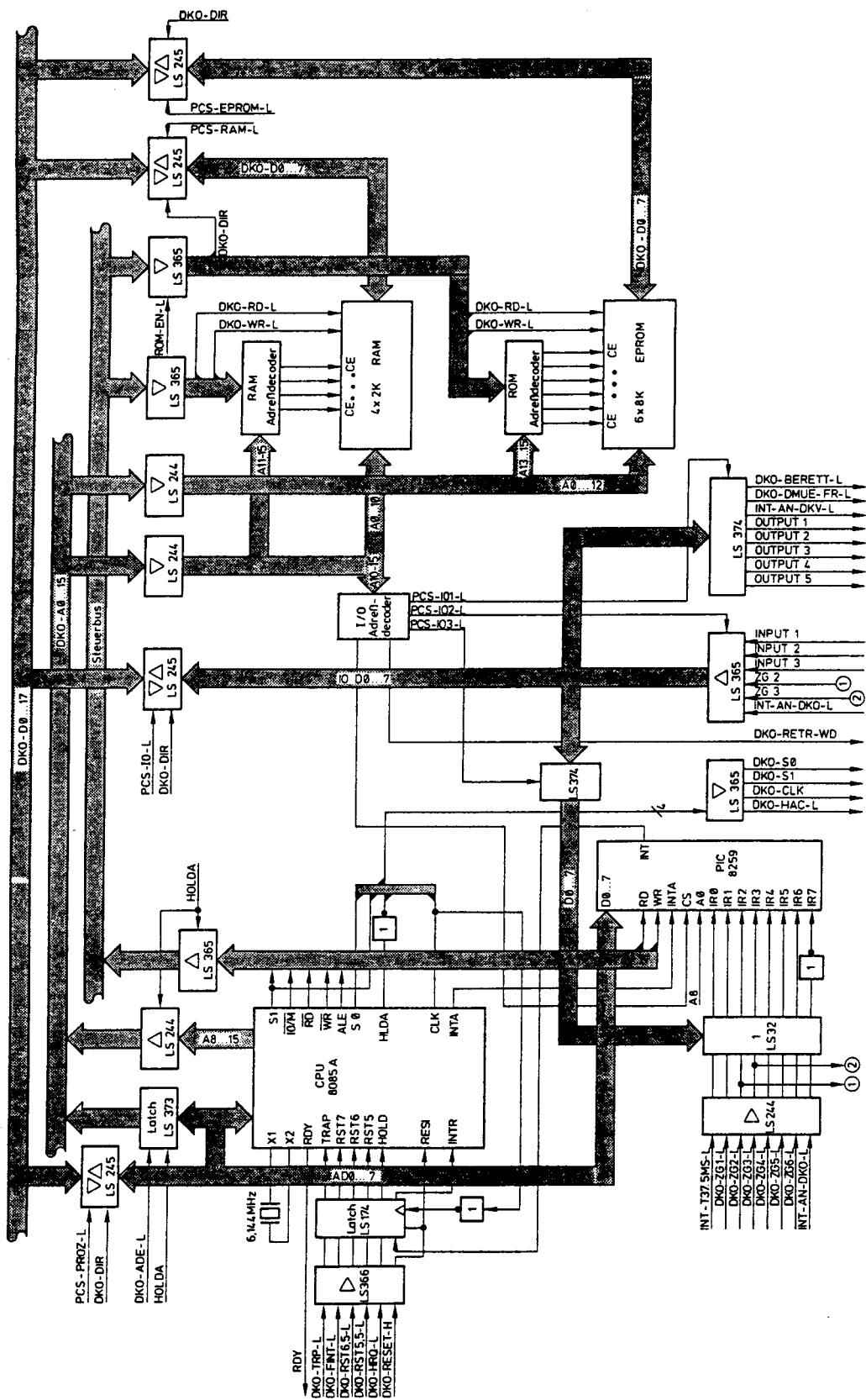

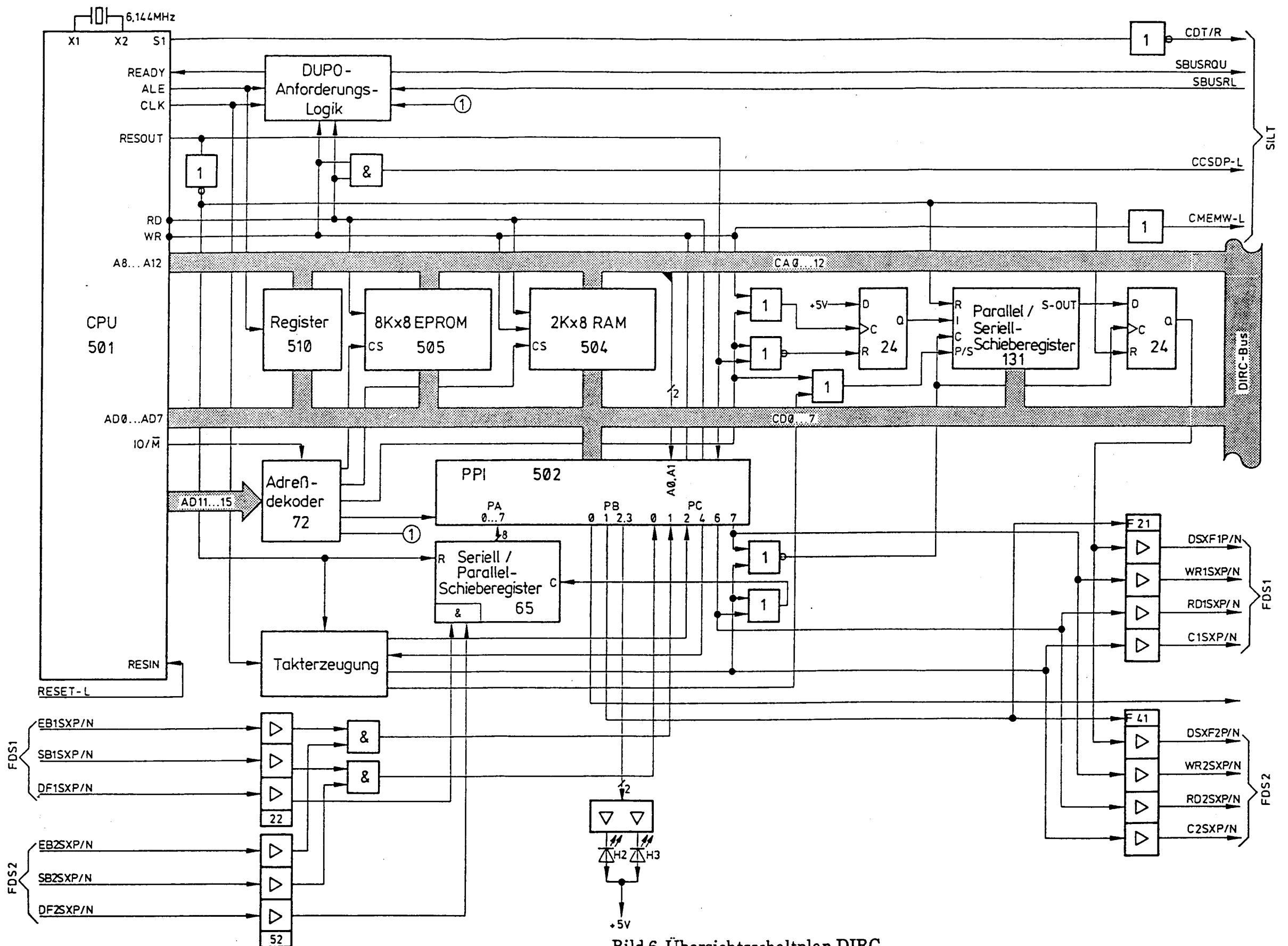

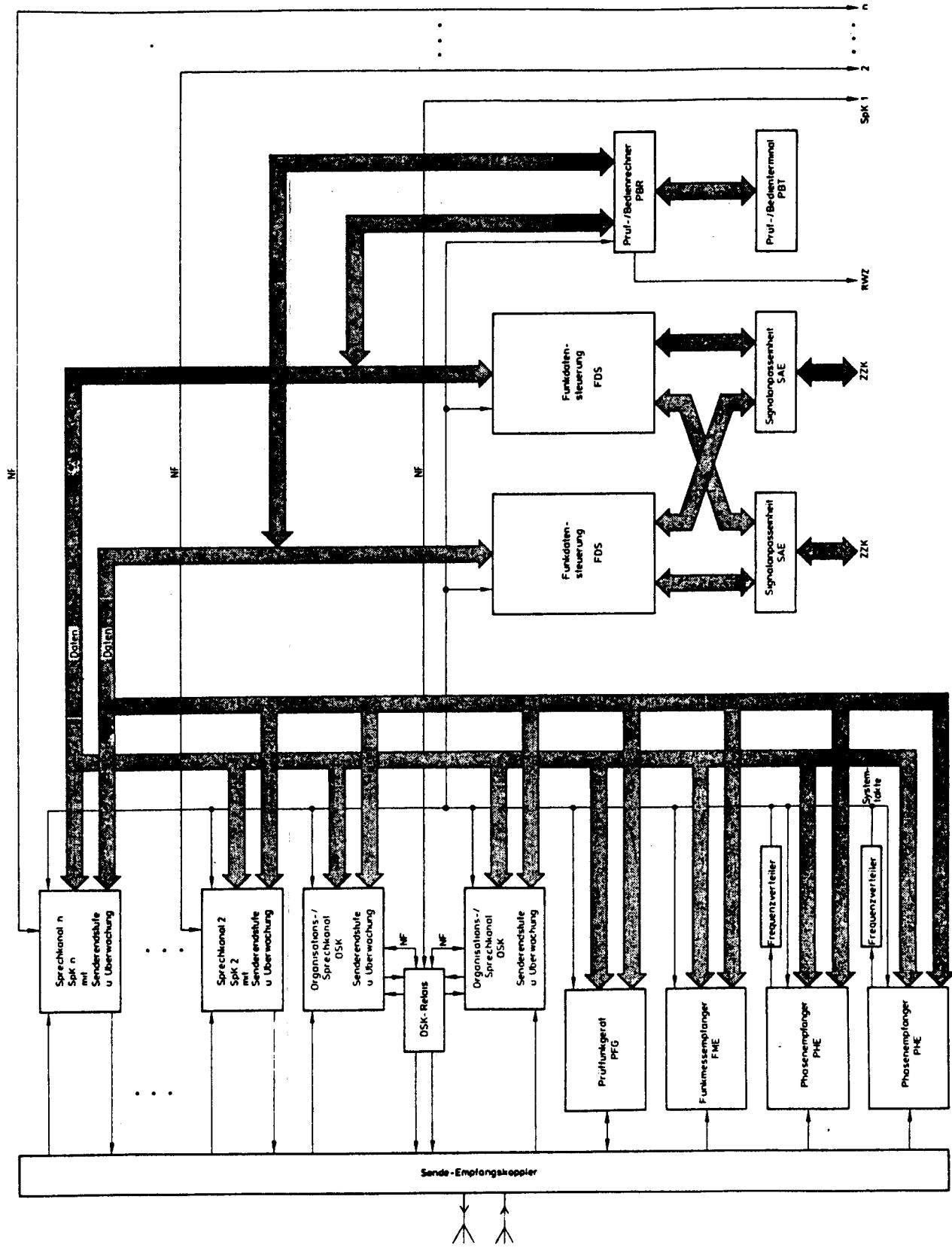

##### **3.1.1 DKo-Prozessor S42024-H179-D1**

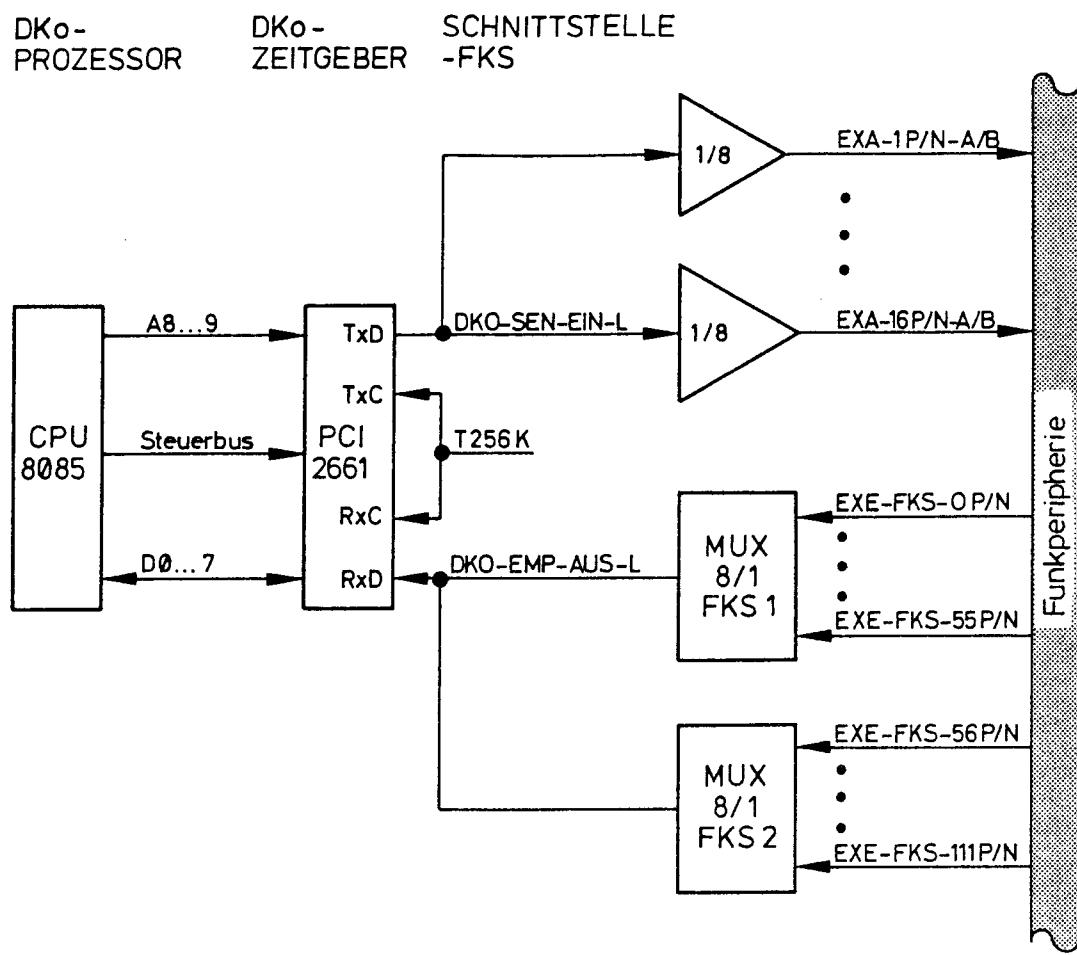

Der Datenkonzentrator (DKo) ist der Schnittstellenrechner der FDS. Er konzentriert die Schnittstellensignale der angeschlossenen Geräte zu Meldungen, die über DMA in die DKV gesendet oder von dort empfangen werden.

Der DKo bedient folgende Schnittstellen:

- serielle Schnittstellen (256 kBaud) zu Funkperipherie und PBR

- serielle Schnittstelle zur SAE

- DMA-Schnittstelle zur DKV.

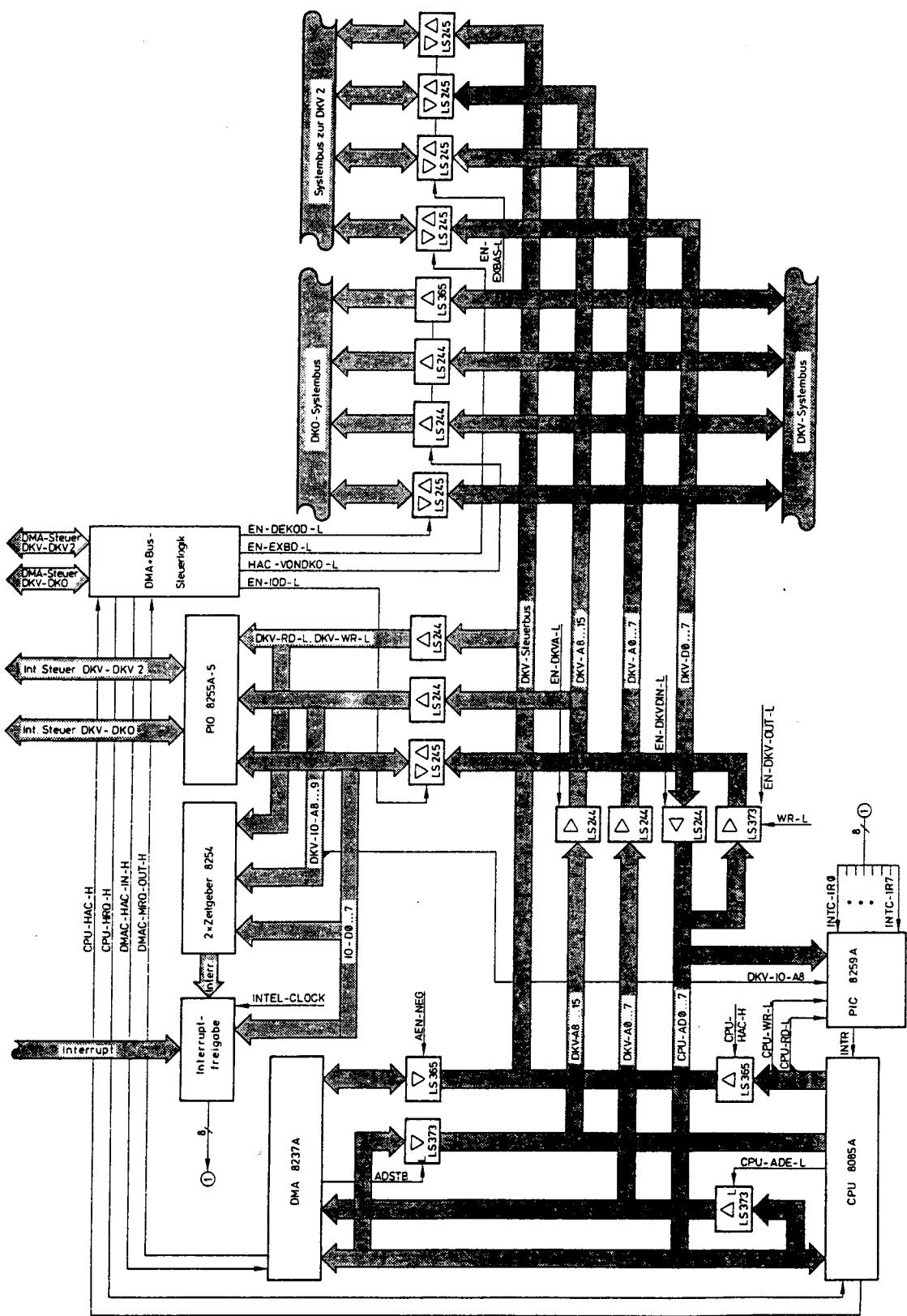

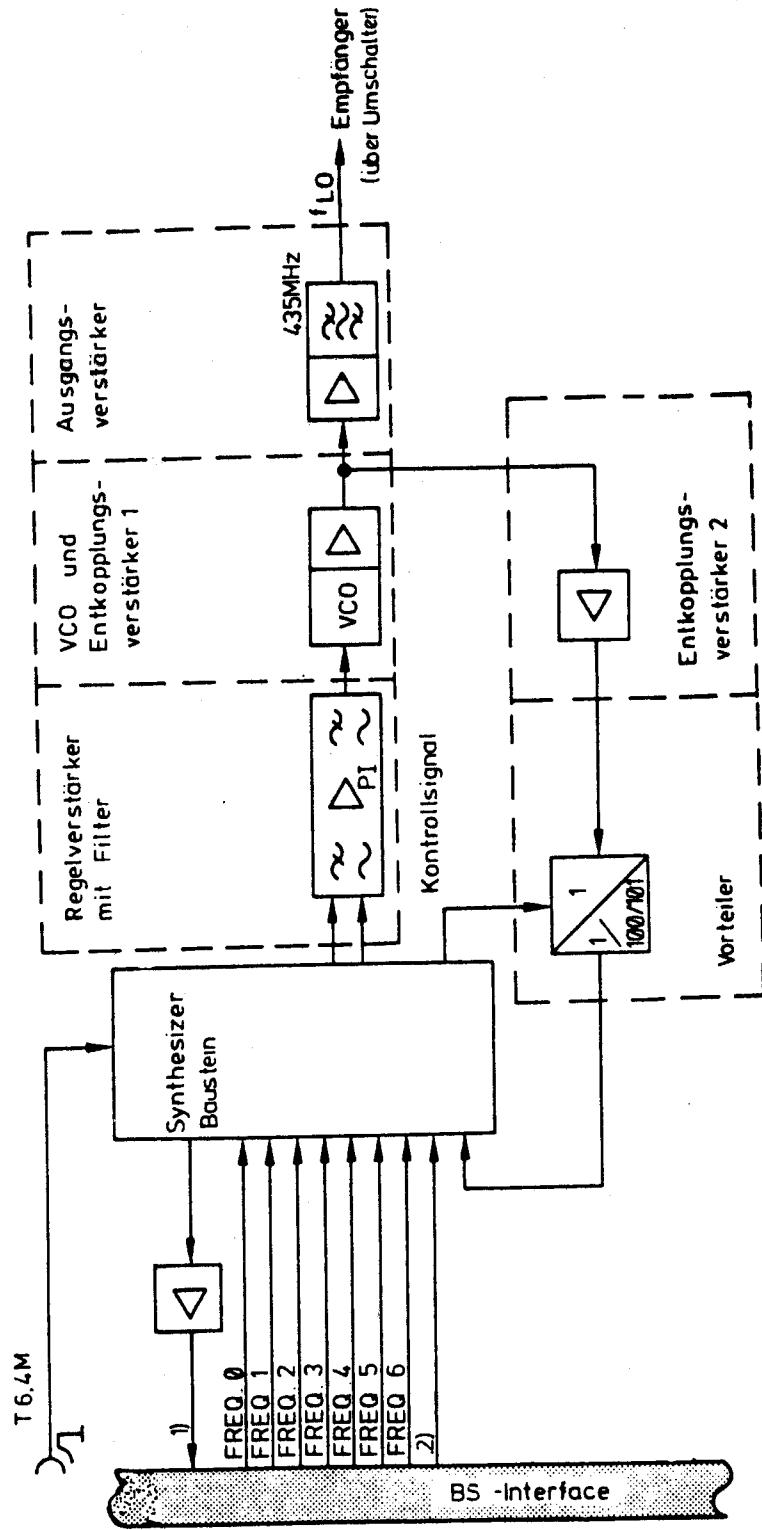

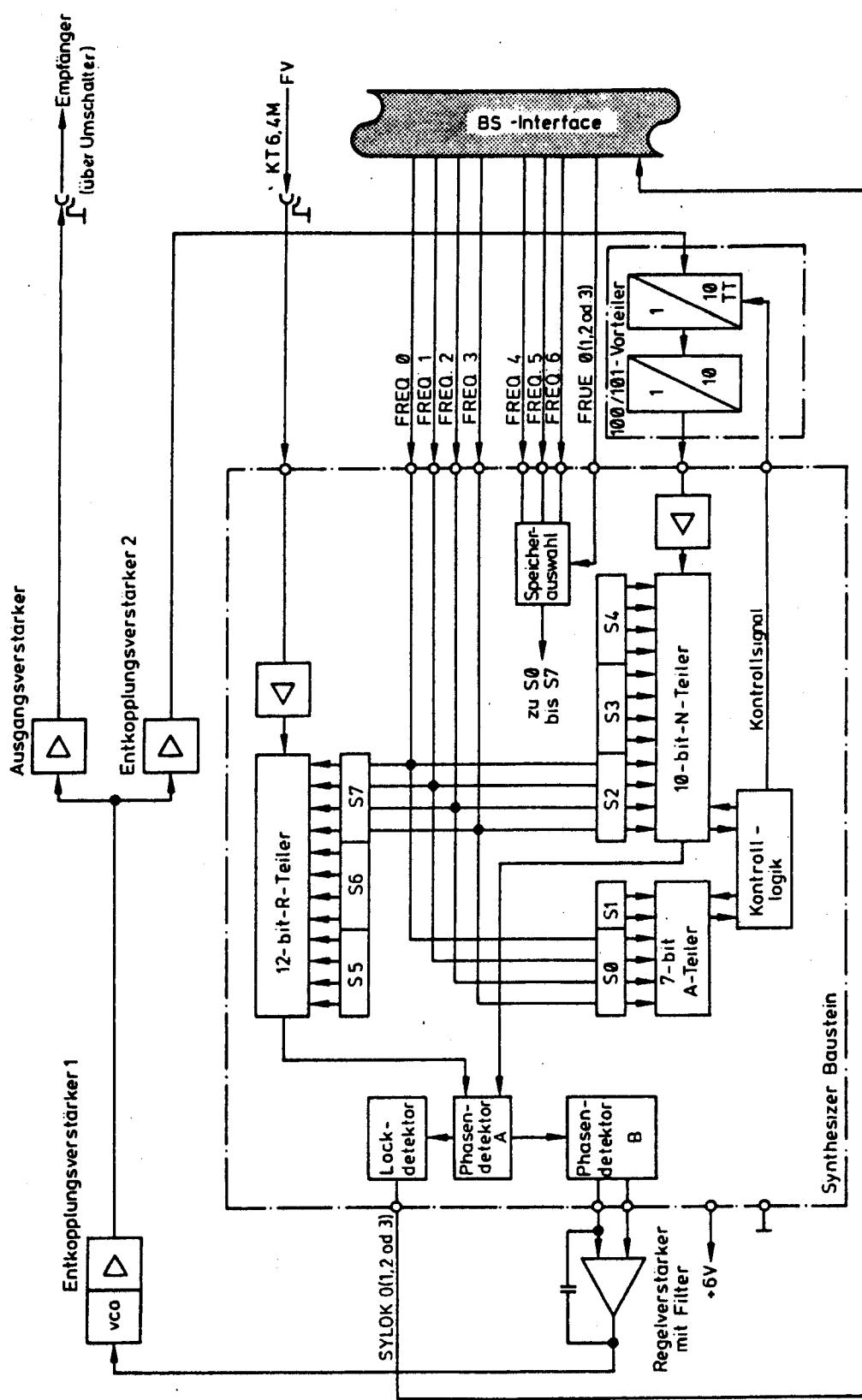

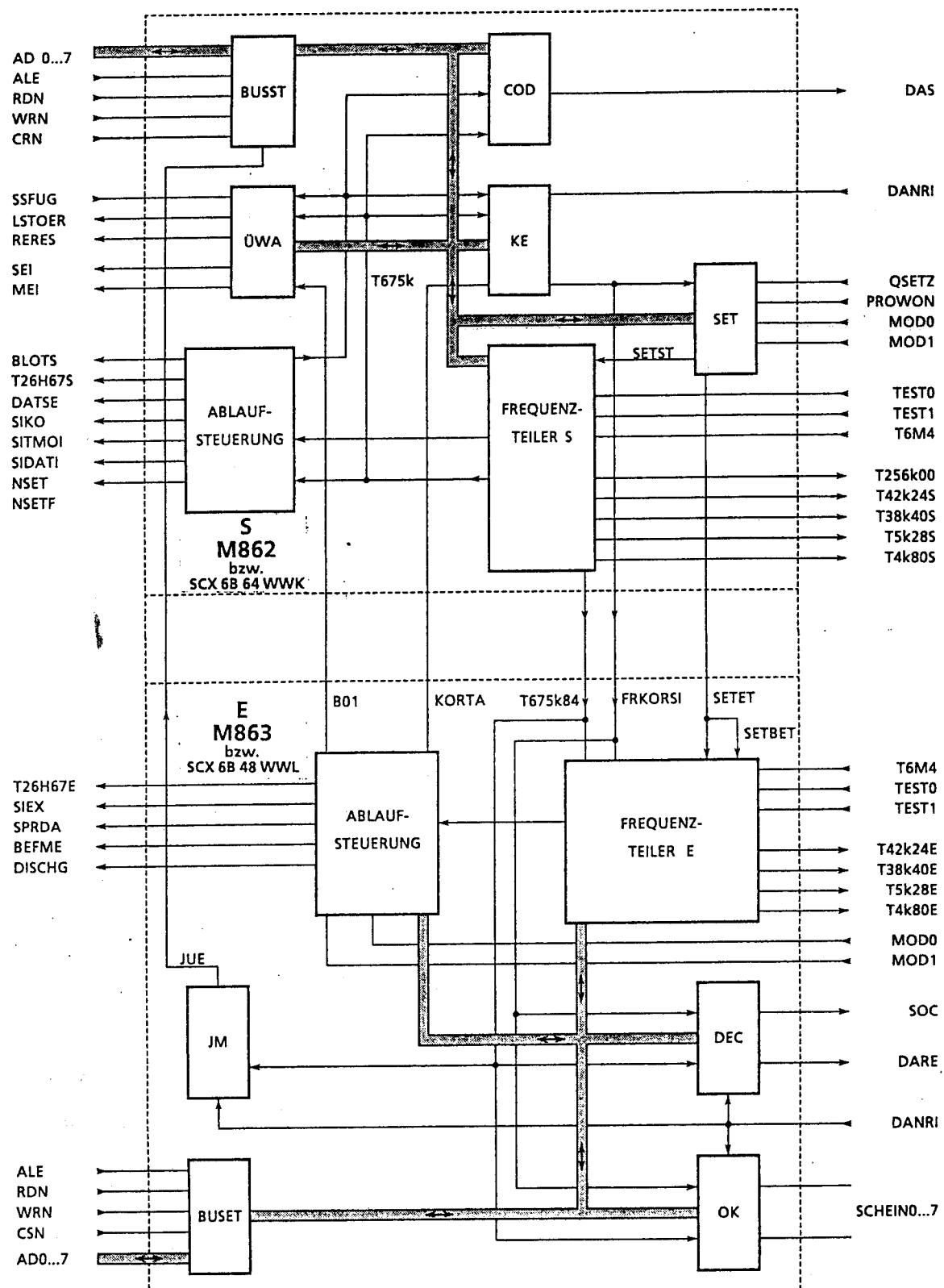

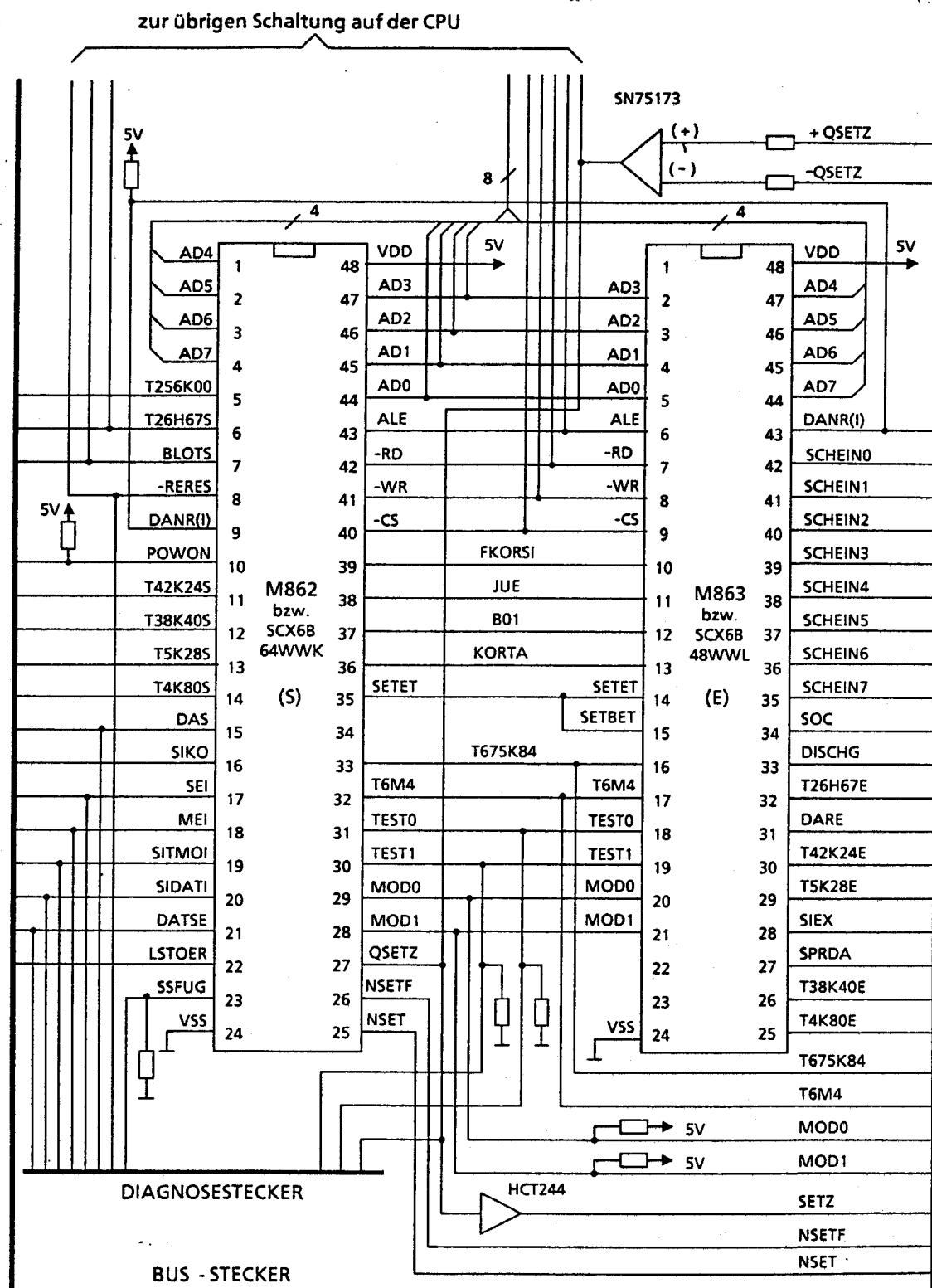

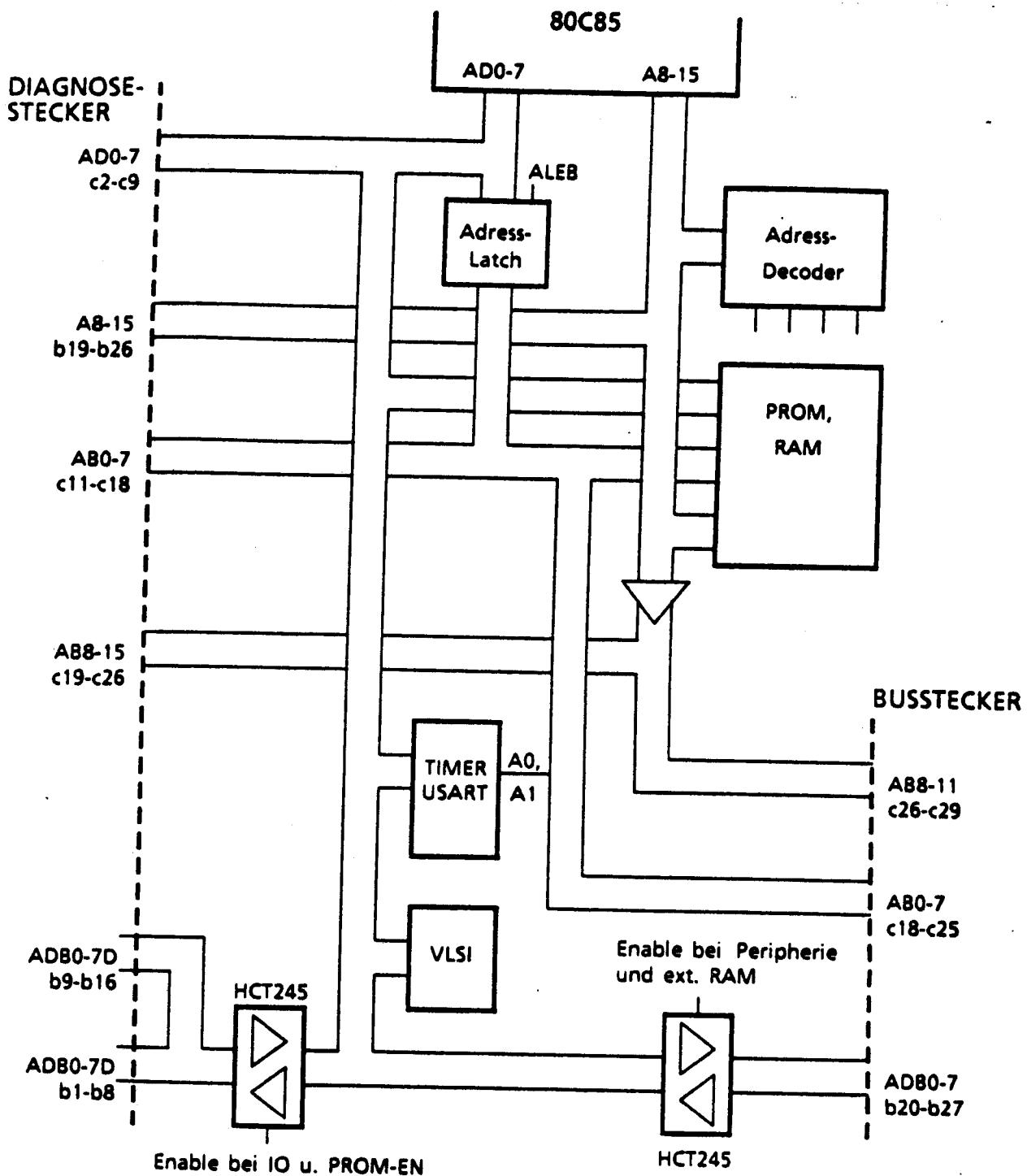

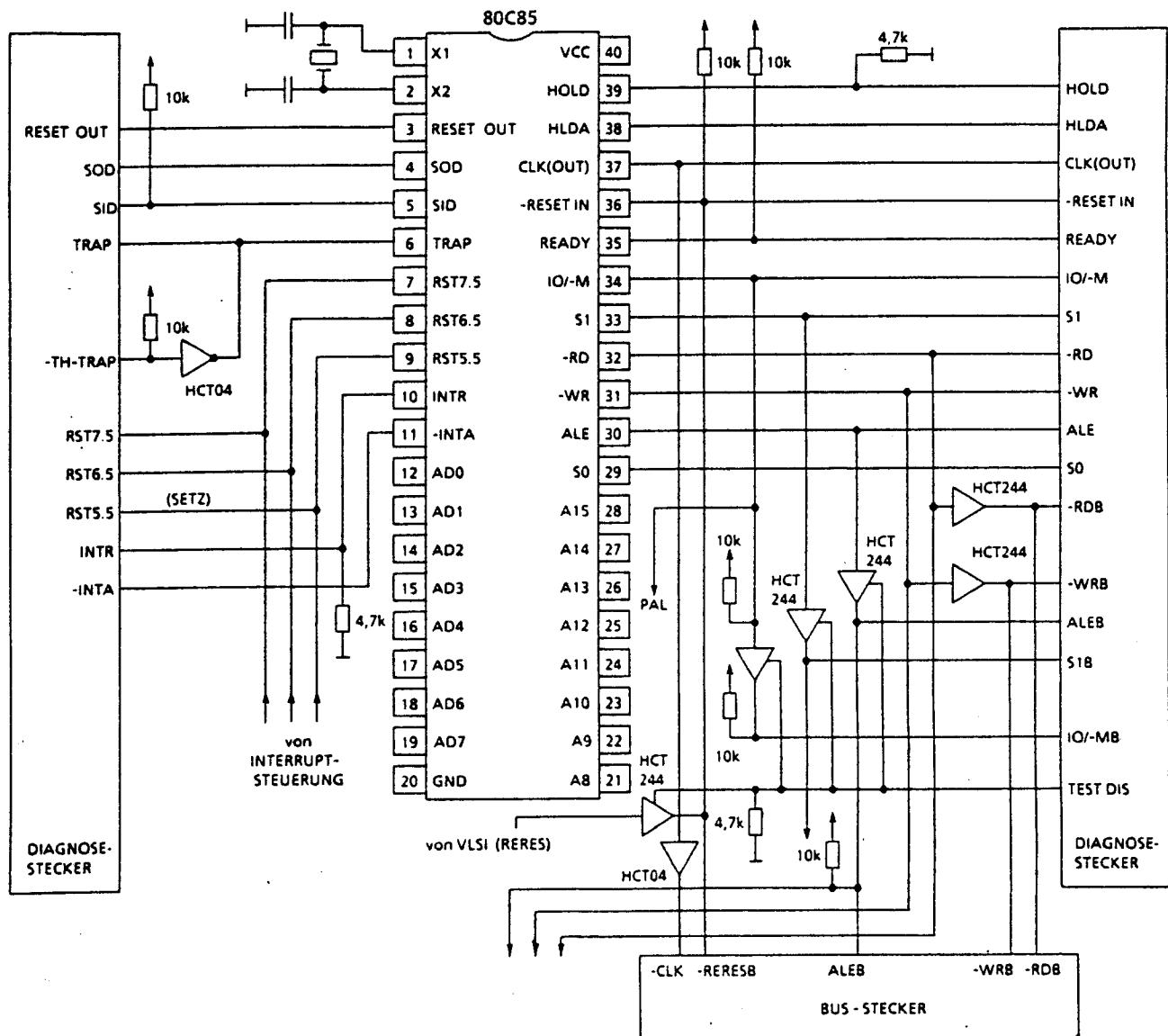

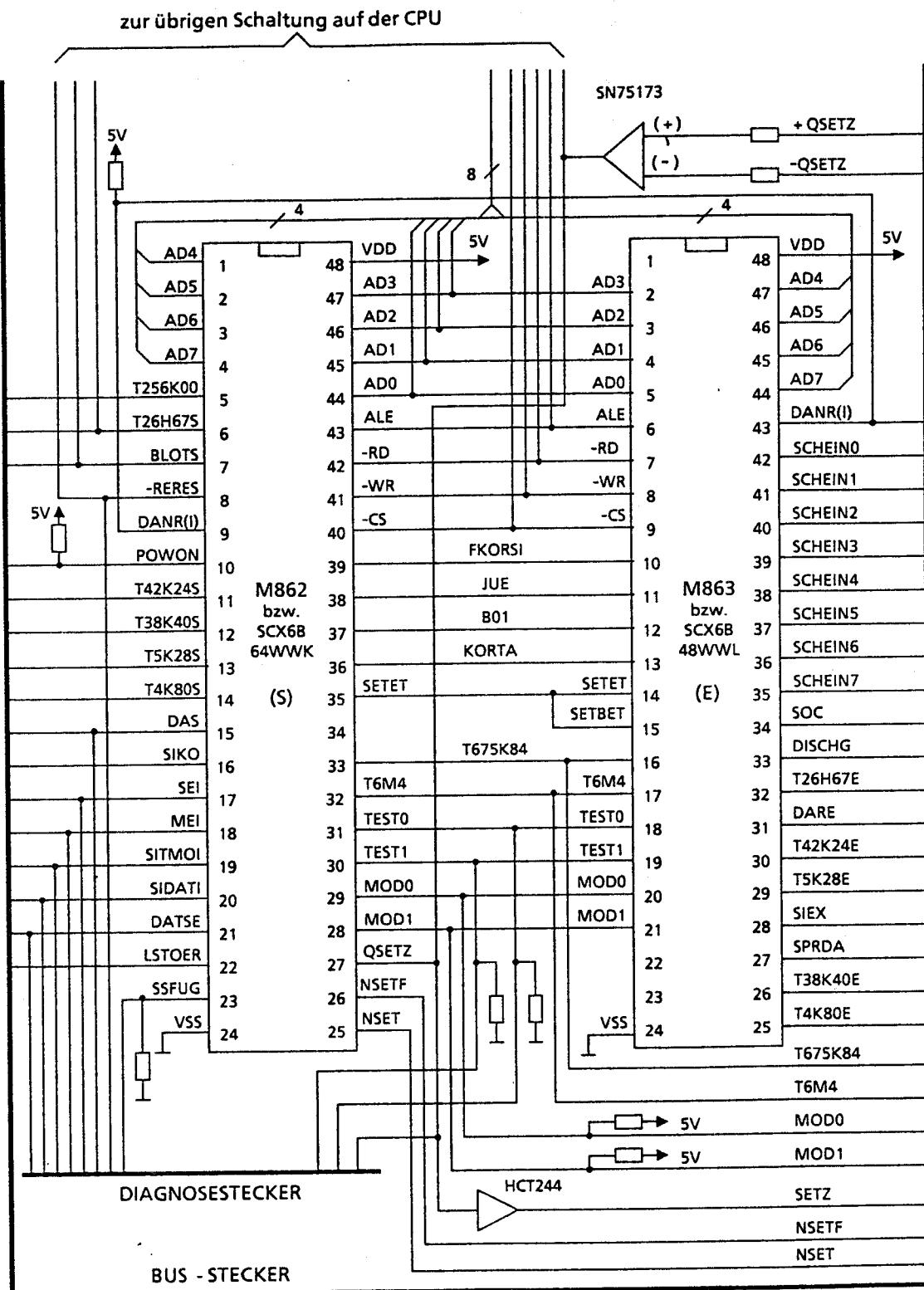

Der DKo besteht aus folgenden wesentlichen Funktionsgruppen (siehe Bild 8):

- CPU 8085 A

- Interrupt-Steuerung PIC 8259

- I/O-Adreßdecoder

- Speicheradreßdecoder

- Speicher (8K-RAM, 48K-EPROM).

Alle freien Eingänge sind mit Pull-Up-Widerständen versehen und auf die Rückwand geführt.

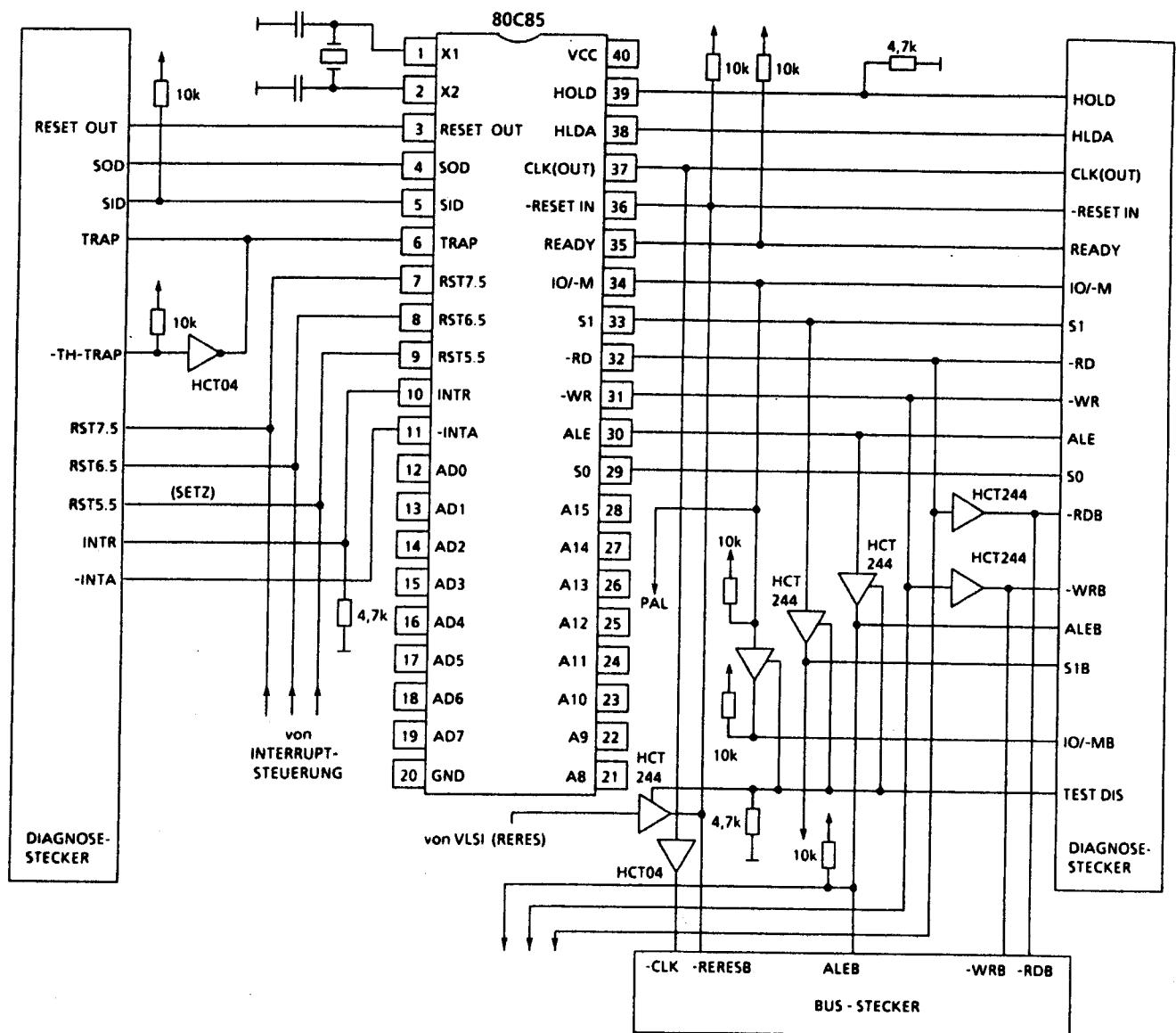

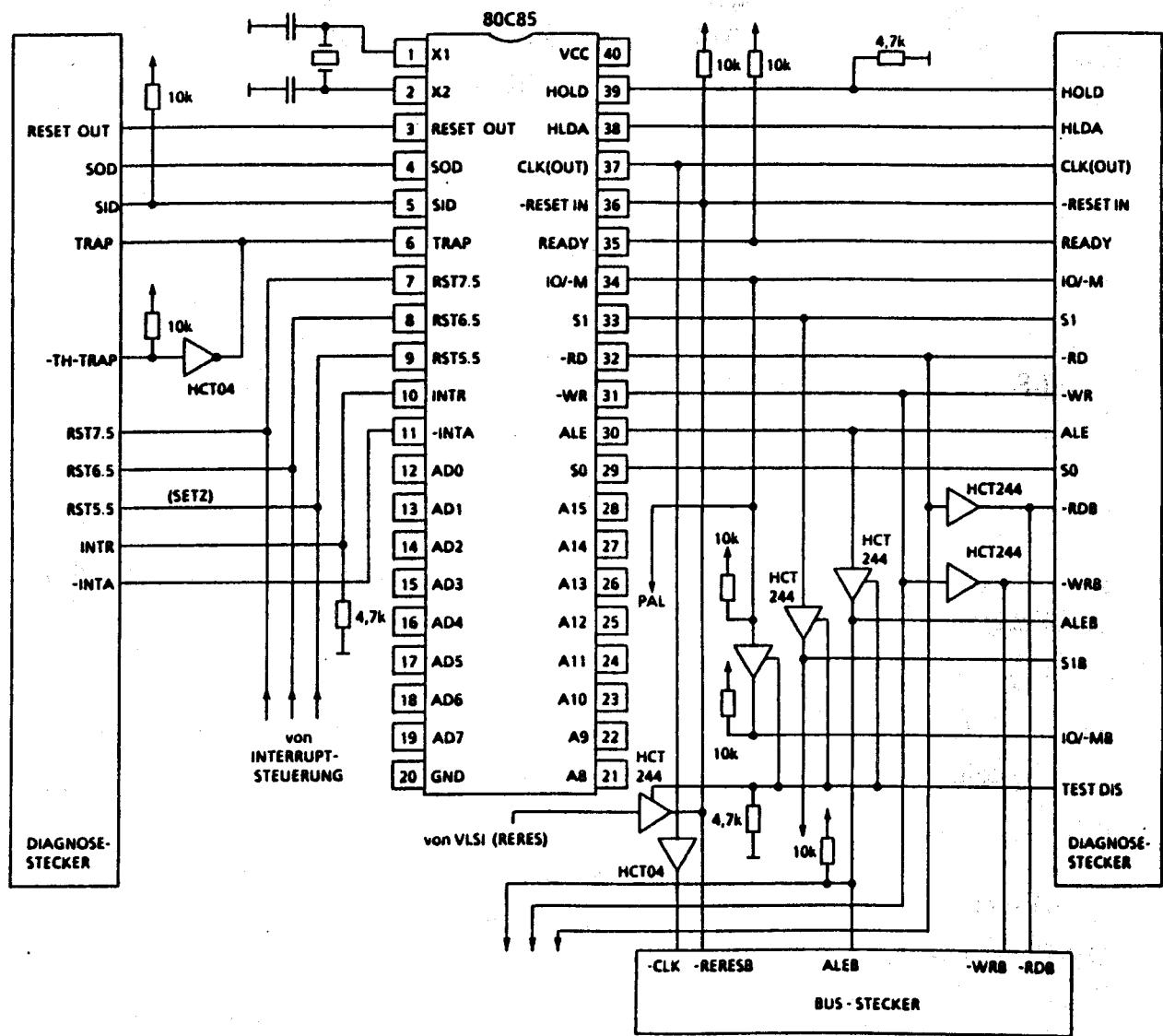

##### **3.1.1.1 CPU**

Die CPU 8085 A wird mit einem 6,144-MHz-Takt betrieben. Sie ist durch einen 16-bit-Adreß-, 8-bit-Daten- und 5-bit-Steuerbus an den DKV-Systembus und die internen Funktionsgruppen angeschlossen.

Die CPU erzeugt folgende Steuersignale, die zum DKo-Steuerbus zusammengefaßt sind:

|      |           |                                  |

|------|-----------|----------------------------------|

| S1   | DKO-DIR   | Datenrichtung einstellbar        |

| ALE  | DKO-ADE-L | Datenbustreiber freigeben        |

| I0/M | DKO-MEN-L | Daten aus Speicher oder I/O-Port |

| RD   | DKO-RD-L  | Daten lesen                      |

| WR   | DKO-WR-L  | Daten schreiben.                 |

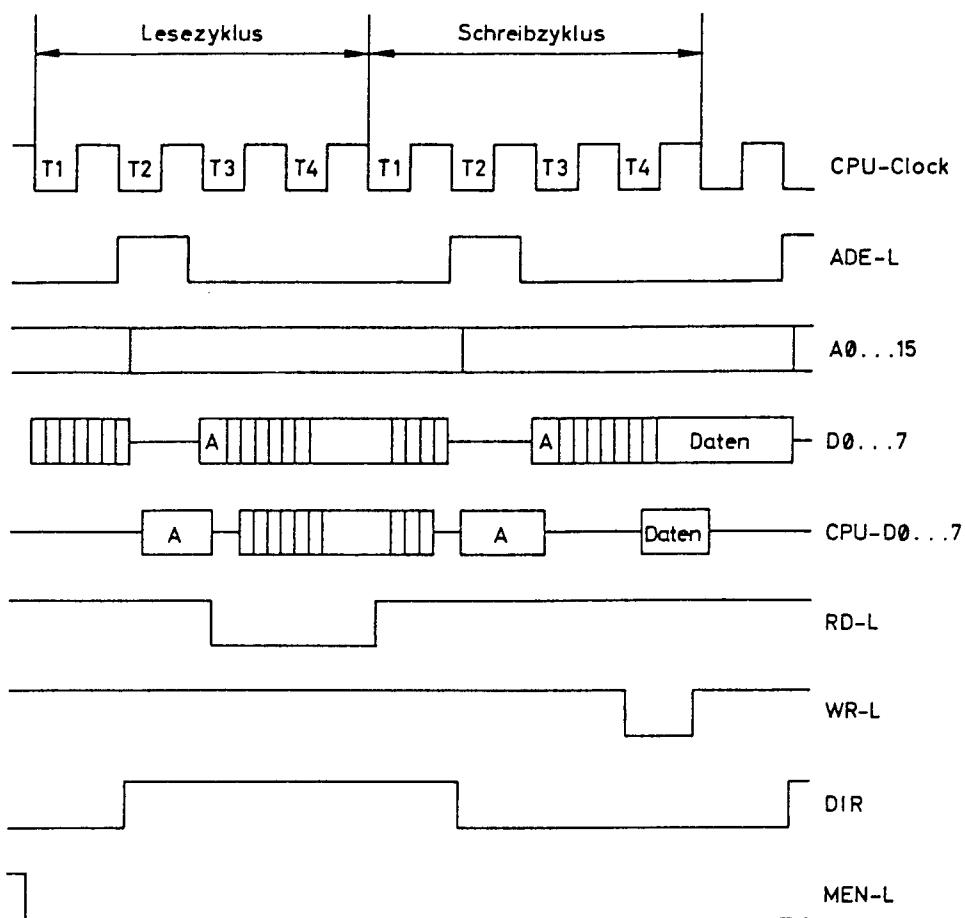

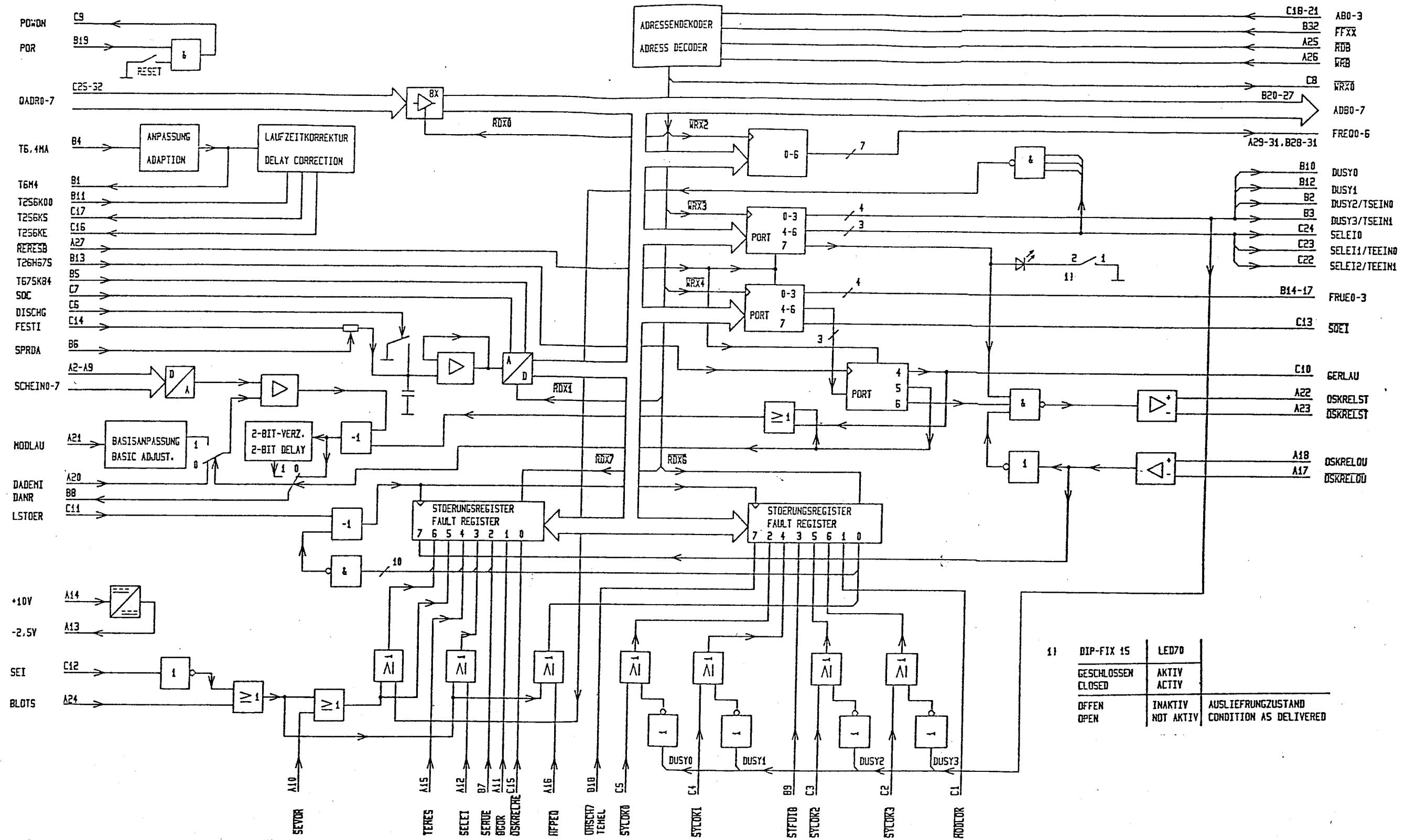

Bild 8 Übersichtsschaltplan DKo-Prozessor

Bild 9 Zeitablauf DKo-Systembus

Daneben ist die CPU noch durch folgende Steuersignale mit den anderen Funktionsgruppen der FDS verbunden:

- DKO-S0 - DKO-RESET-H

- DKO-S1 - DKO-HRQ

- DKO-CLK - DKO-TRAP

- DKO-FINT-L

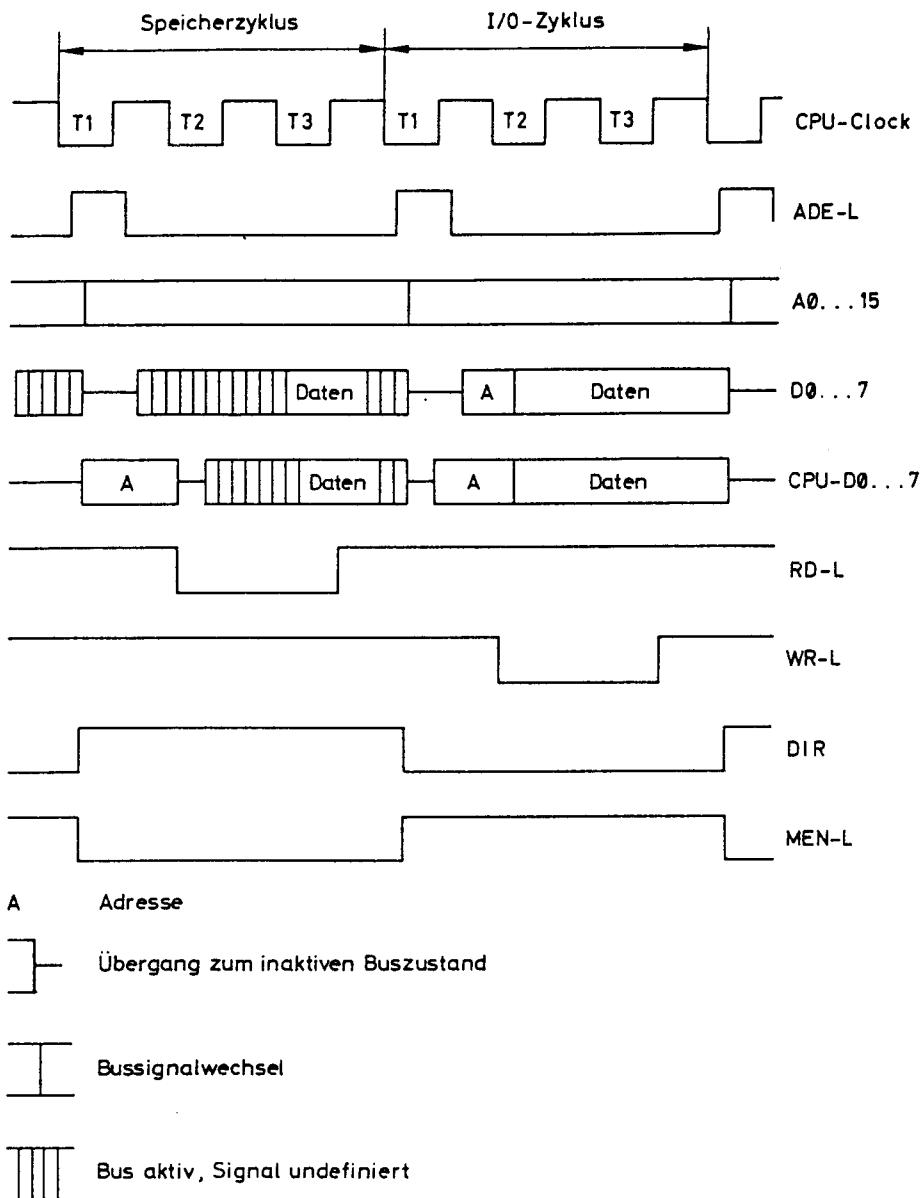

Zum DKo-Systembus werden alle Signale über Treiber geschaltet. In Bild 9 ist der Zeitablauf auf dem DKo-Systembus oder CPU-Bus beim Datenaustausch dargestellt.

#### Ablauf Lesezyklus:

- DKO-ADE-L = 1 Datenbustreiber gesperrt

DKO-AD0...7 niederwertige Adresse auf CPU-Bus

- DKO-DIR = 1 Datenrichtung einstellen

- DKO-ADE-L = 0 angesprochene, externe Datenbustreiber freigeben

- DKO-RD-L = 0 CPU-Bustreiber freigeben, Daten von DKo-Systembus auf CPU-Bus

- DKO-RD-L = 1 Daten lesen, CPU-Bustreiber sperren

- DKO-ADE-L = 1 Datenbustreiber gesperrt

#### Ablauf Schreibzyklus:

- DKO-ADE-L = 1 Datenbustreiber gesperrt

DKO-AD0...7 niederwertige Adresse auf CPU-Bus

- DKO-DIR = 1 Datenrichtung einstellen

- DKO-ADE = 0 angesprochene Datenbustreiber freigeben

- DKO-WR-L = 0 Daten von CPU auf DKo-Systembus

- DKO-WR-L = 1 Schreiben beendet

- DKO-ADE-L = 1 Datenbustreiber gesperrt

Die CPU wird durch DKO-RESET-H von der FDS-Sicherheitstechnik rückgesetzt. Durch DKO-BEREIT-L wird der DKV die Betriebsbereitschaft mitgeteilt. Das Ausbleiben von DKO-BEREIT-L wird auf der Baugruppe Sicherheit FDS mittels LED angezeigt.

Das Signal DKO-TRAP-L erzeugt einen nichtmaskierbaren Interrupt zu Diagnosezwecken.

Von der Baugruppe Sicherheit FDS wird ein Fehlerinterrupt gebildet, der mittels DKV-FINT-L an RST 7,5 der CPU signalisiert wird. Die Interrupteingänge RST 6,5 und RST 5,5 sind nicht beschaltet. Die Übernahme der Interrupts aus dem Latch LS174 wird mit der negativen Flanke des Signals DKO-CLK vorgenommen.

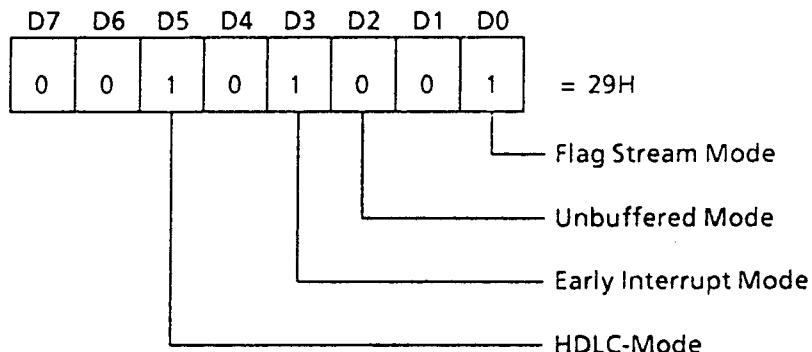

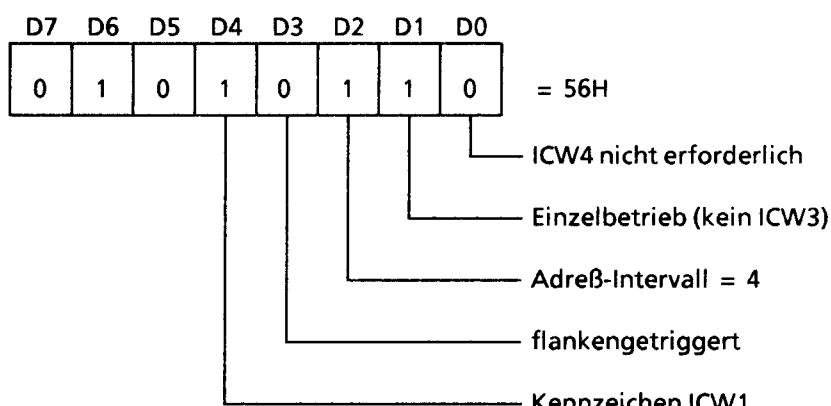

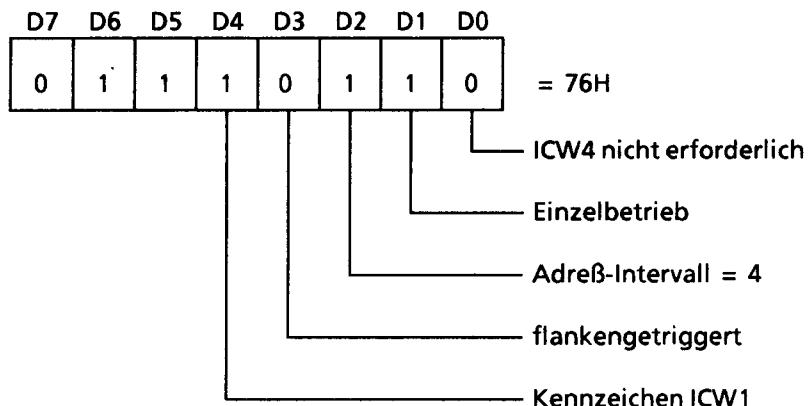

#### 3.1.1.2 Interrupt-Steuerung PIC

Die Interrupt-Steuerung ist mit dem Baustein 8259 (Adresse 30H) realisiert, der am CPU-Datenbus angeschlossen ist.

Über INTA meldet die CPU den Empfang eines vom PIC über INT gesendeten Interrupts.

Tabelle 3 Beschaltung der Eingänge des PIC

| Signal         | Eingang | Bedeutung                                                                 |

|----------------|---------|---------------------------------------------------------------------------|

| INT-T37, 5MS-L | IR0     | Funkblock-Interrupt des DKo-Zeitgebers,<br>Taktperiode des 256-kHz-Taktes |

| DKO-ZG1-L      | IR1     | Zeitgeber 1, Zähler 0                                                     |

| DKO-ZG2-L      | IR2     | Zeitgeber 1, Zähler 1                                                     |

| DKO-ZG3-L      | IR3     | Zeitgeber 1, Zähler 2                                                     |

| DKO-ZG4-L      | IR4     | Zeitgeber 2, Zähler 0                                                     |

| DKO-ZG5-L      | IR5     | Zeitgeber 2, Zähler 1                                                     |

| DKO-ZG6-L      | IR6     | Zeitgeber 2, Zähler 2                                                     |

| INT-AN-DKO-L   | IR7     | DMA-Übertragung, von DKV                                                  |

Alle Interrupt-Signale des DKo-Zeitgebers, DKO-ZG1-L...6-L, INT-T37.5MS-L und INT-AN-DKO-L, werden LOW-aktiv zur Interrupt-Steuerung des DKo-Prozessors übertragen. Diese Eingangssignale sind mit Pull-Up-Widerständen versehen. Der PIC 8259 reagiert auf die positive Flanke (Rückflanke) dieser Eingangssignale. Das Signal INT-AN-DKO-L vom DKV-Prozessor wird negiert und ist mit der Vorderflanke aktiv.

Das Signal INT-AN-DKV-L wird vom DKV-Output-Port (LS 365 Adresse 64H) Bit 0 gesendet und stellt die Anforderung für einen DMA-Zyklus.

Die acht Interruptsignale die an die Interrupt-Steuerung herangeführt sind, können vom Interrupt-Freigabe-Latch (Adresse LS 374, 68H) einzeln gesperrt oder freigegeben werden.

Bedeutung der Bits vom Interrupt-Freigabe-Latch:

Freigabe: 0

Sperre: 1

- I0-D0 INT-T37.5MS-L

- I0-D1 DKO-ZG1-L

- I0-D2 DKO-ZG2-L

- I0-D3 DKO-ZG3-L

- I0-D4 DKO-ZG4-L

- I0-D5 DKO-ZG5-L

- I0-D6 DKO-ZG6-L

- I0-D7 INT-AN-DKO-L

Beim Sperren und Freigeben können vier Fälle auftreten:

- Der Interrupt ist maskiert:

Das Interruptsignal ist unwirksam und wird nicht gespeichert.

- Der Interrupt wird freigegeben:

Der Vorgang "Freigabe des Interrupts" hat keine Auswirkung.

- Der Interrupt ist freigegeben:

Der Interrupt wird mit der Rückflanke des Interrupt-Signals wirksam und gespeichert, ausgenommen INT-AN-DKO-L, das mit der Vorderflanke wirksam und gespeichert wird.

- Der Interrupt wird gesperrt:

Wenn das Interrupt-Signal anliegt, wird der Interrupt beim Sperren wirksam und wird gespeichert. Das gilt nicht für INT-AN-DKO-L.

### 3.1.1.3 I/O-Adreßdecoder

Der I/O-Adreßdecoder liefert die Adressen für die Parallel I/O-Ports, die Belegung der Interruptsperre und das Retriggern des Watchdogs. Decodiert wird aus den Adreßbits DKO-A10...15 des DKo-Systembusses.

- Adresse 60H – 63H Output-Port

- Adresse 68H – 6BH Output-Port

- Adresse 6CH – 6FH Output-Port

- Adresse 64H – 67H Input-Port.

Im DKo-Prozessor wird die direkte I/O-Adressierung angewendet, d.h. die Ports werden unmittelbar über den Adreßbus mit den entsprechenden Steuerleitungen adressiert. Es stehen 256 I/O-Adressen zur Verfügung. Diese Adressen werden durch acht Adreßleitungen unterschieden. Bei I/O-Zugriff ist das Signal MEN-L logisch 1 und die acht Adreßbits erscheinen sowohl auf dem niederwertigen (A0...7) als auch auf dem höherwertigen (A8...15) Adreßbus. Die 256 Adressen werden in 16 Adreßblöcke zu je 16 Adressen unterteilt. Jeder Adreßblock wird einer Einheit (Baugruppe oder Baustein) zugeordnet. Innerhalb dieses Adreßblocks können die Adressen frei vergeben werden. Die Adreßblöcke werden durch die Adreßbits A4 bis A7 bzw. A12 bis A15 unterschieden. Die Decodierung geschieht für die Baugruppen oder Bausteine dezentral.

Tabelle 4 I/O-Adressierung

| Adresseblock | Adressen    | Einheit                                |

|--------------|-------------|----------------------------------------|

| 0            | 00H bis OFH | Serielle Schnittstelle (USART 2661-3I) |

| 1            | 10H bis 1FH | Kanalauswahl für Schnittstelle-FKS     |

| 2            | 20H bis 2FH | Ports Sicherheitstechnik               |

| 3            | 30H bis 3FH | Interrupt-Steuerung PIC 8259           |

| 4            | 40H bis 4FH | DKo-Zeitgeber 2                        |

| 5            | 50H bis 5FH | DKo-Zeitgeber 1                        |

| 6            | 60H bis 6FH | Ports DKo-Prozessor                    |

| 7            | 70H bis 7FH | DKo-Zeitgeber 0                        |

| 8            | 80H bis 8FH | reserviert für Zusatzeinrichtungen     |

| 9            | 90H bis 9FH | reserviert für Zusatzeinrichtungen     |

| 10           | A0H bis AFH | reserviert für Zusatzeinrichtungen     |

| 11           | BOH bis BFH | frei                                   |

| 12           | COH bis CFH | frei                                   |

| 13           | DOH bis DFH | frei                                   |

| 14           | EOH bis EFH | Schnittstelle ZZK                      |

| 15           | FOH bis FFH | Schnittstelle ZZK                      |

### 3.1.1.4 Parallel-I/O-Ports

- Handshake, Output

Adresse: 60H

Vom Output-Port werden gesendet:

- Bit 0 DKO-BEREIT-L

- Bit 1 DKO-DMUE-FR-L

- Bit 2 INT-AN-DKV-L

Die Bits 3 bis 7 sind nicht beschaltet.

DKO-BEREIT-L wird benutzt um der DKV den Bereitzustand mitzuteilen.

DKO-DMUE-FR-L dient dazu der DKV zu signalisieren, daß der DKo zur DMA-Übertragung freigegeben ist.

- Handshake, Input

Adresse: 64H

Über das Parallel-Input-Port können die in Tabelle 5 genannten Signale abgefragt werden.

Tabelle 5 Belegung Input-Port

| Bit | Signalname   | Wert | Funktion                                                            |

|-----|--------------|------|---------------------------------------------------------------------|

| 0   | INT-AN-DKO-L | 0    | der Interrupt von DKV an den DKo ist aktiv                          |

|     |              | 1    | inaktiv                                                             |

| 1   | DKO-ZG2      | 0    | Interruptsignal von Zeitgeber 1 (Zähler 2) ist aktiv (OUT 1 = 0)    |

|     |              | 1    | inaktiv                                                             |

| 2   | DKO-ZG3      | 0    | Interruptsignal vom Zeitgeber 1 (Zähler 3) ist aktiv (OUT 2 = 0)    |

|     |              | 1    | inaktiv                                                             |

| 3   | INPUT1       | 0    | kann durch am Diagnosestecker angesteckte Hardware definiert werden |

|     |              | 1    | Diagnosestecker nicht belegt                                        |

| 4   | INPUT2       | 0    | kann durch am Diagnosestecker angesteckte Hardware definiert werden |

|     |              | 1    | Diagnosestecker nicht belegt                                        |

| 5   | INPUT3       | 1    | frei, logisch 1                                                     |

- Belegung Interruptsperre

Adresse: 68H

PCS-103-L wird mit Adresse 68H von I/O-Decoder gebildet und beschaltet den CLOCK-Eingang der Interrupt-Sperre (LS 374).

- Retriggern Watchdog

Adresse: 6CH

Durch Befehl OUT 6CH wird ein Retriggern des Watchdogs (DKO-RETR-WD-L) ausgelöst.

### 3.1.1.5 Speicheradreßdecoder

- RAM-Adreßdecoder

Mit Hilfe des RAM-Adreßdecoders werden die Adressen für den 8K-RAM-Speicher decodiert. Die Decodierung wird in 2K-Bereichen für die vier Speicherbausteine aus den Adreßbits DKO-A10...15 vorgenommen. Der RAM-Adreßbereich C000H bis DFFFH gliedert sich somit in vier Teilbereiche.

Aufteilung der Adreßbereiche:

- C000H...C7FFH

- C800H...CFFFH

- D000H...D7FFH

- D800H...DFFFHB08

- ROM-Adreßdecoder

Der ROM-Adreßdecoder decodiert aus den Adreßbits DKo A13...15 den Adreßbereich 0000H...BFFFH. Damit werden die 8K-Bereiche des 48K-EPROM-Speicher freigegeben.

Aufteilung der Adreßbereiche:

- 0000H...1FFFH

- 2000H...3FFFH

- 4000H...5FFFH

- 6000H...7FFFH

- 8000H...9FFFH

- A000H...BFFFH

Der Decoder wird mit DKO-ADE-L, DKO-MEN-L und DKO-HAC-L freigegeben.

### 3.1.1.6 Speicher

Der Speicher des DKo-Prozessors besteht aus einem 8K-RAM- und einem 48K-EPROM-Speicher.

Tabelle 6 Adreßbereichsaufteilung DKo-Prozessor

| Adreßbereich   | Speicher                             |

|----------------|--------------------------------------|

| 0000H...BFFFH  | 48K - EPROM                          |

| C000H...DFFFH  | 8K - RAM                             |

| E000H...F7FFFH | nicht belegt                         |

| F800H...F8FFFH | RAM2 Schnittstelle ZZK, nicht belegt |

| F900H...FBFFFH | RAM2 Schnittstelle ZZK               |

| FC00H...FCFFFH | RAM1 Schnittstelle ZZK, nicht belegt |

| FD00H...FFFFH  | RAM1 Schnittstelle ZZK               |

Der 8K-RAM Speicher ( $4 \times 2$  Kbyte, HM6116) liegt am DKO-Systembus (DKO-A0...10, DKO-D0...7) und wird vom RAM-Decoder gesteuert. DKO-WR-L und DKO-RD-L von der CPU übernehmen die Auswahl eines Schreib- bzw. Lesezyklus. Am 48K-EPROM ( $6 \times 8$  Kbyte, MD2764) liegen die Adreßleitungen DKO-A0...12 und die Datenleitungen DKO-D0...7. Die Steuerung wird über den ROM-Adreßdecoder oder die Steuersignale der CPU vorgenommen. Auf den EPROM-Speicher ist kein DMA-Zugriff möglich. Für Systemtests kann der 48K-EPROM-Bereich mit RAM-Speicherbausteinen bestückt werden. In diesem Fall dient der Schalter S1 zur Freigabe von DKO-WR-L an die RAM-Bausteine.

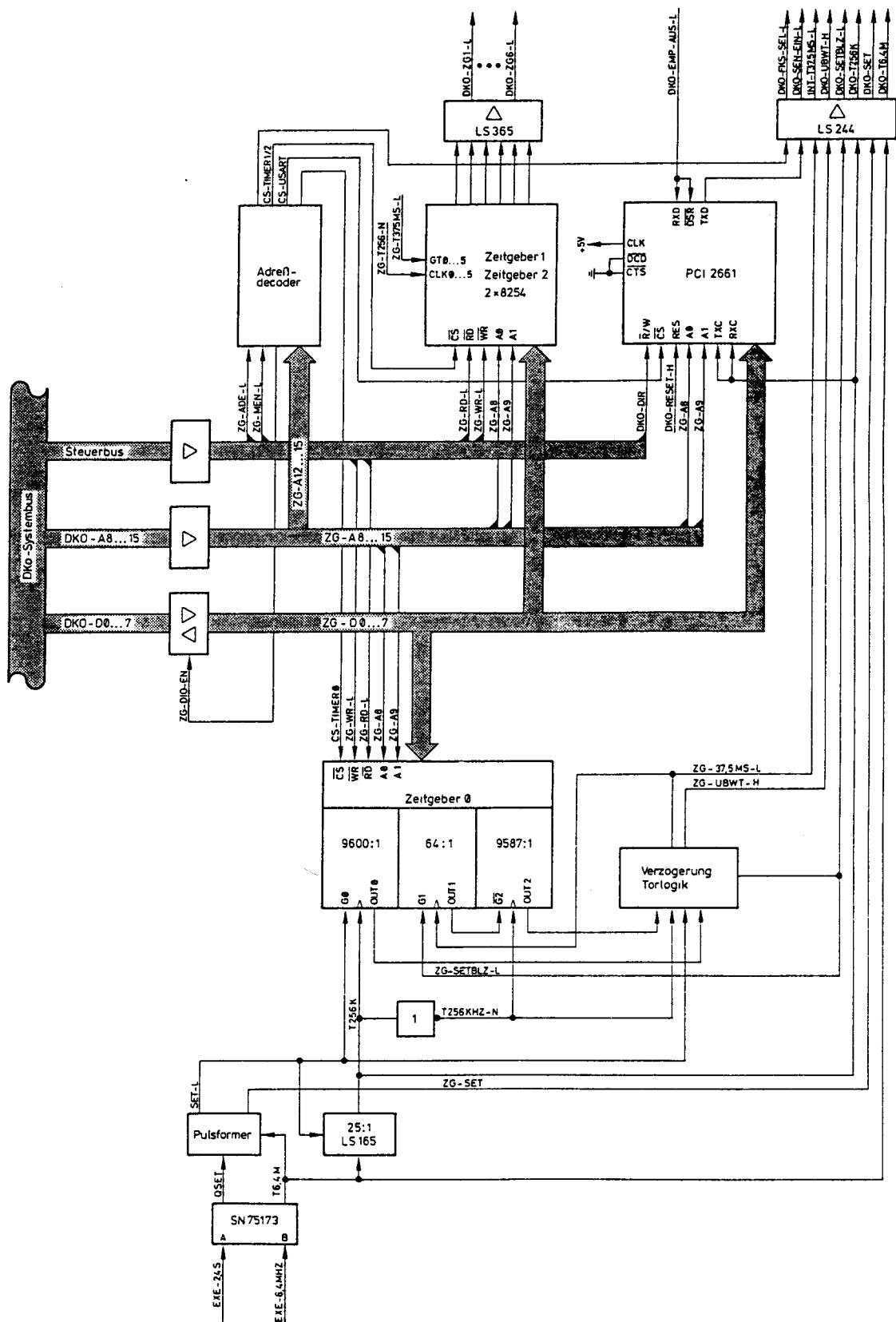

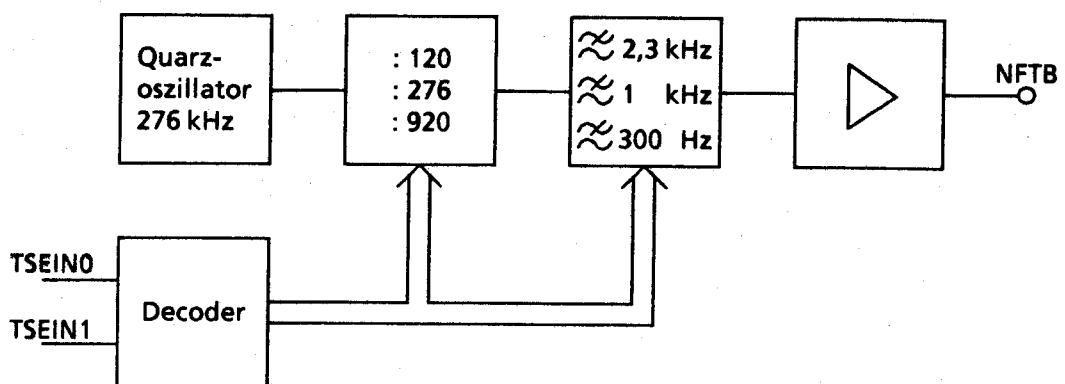

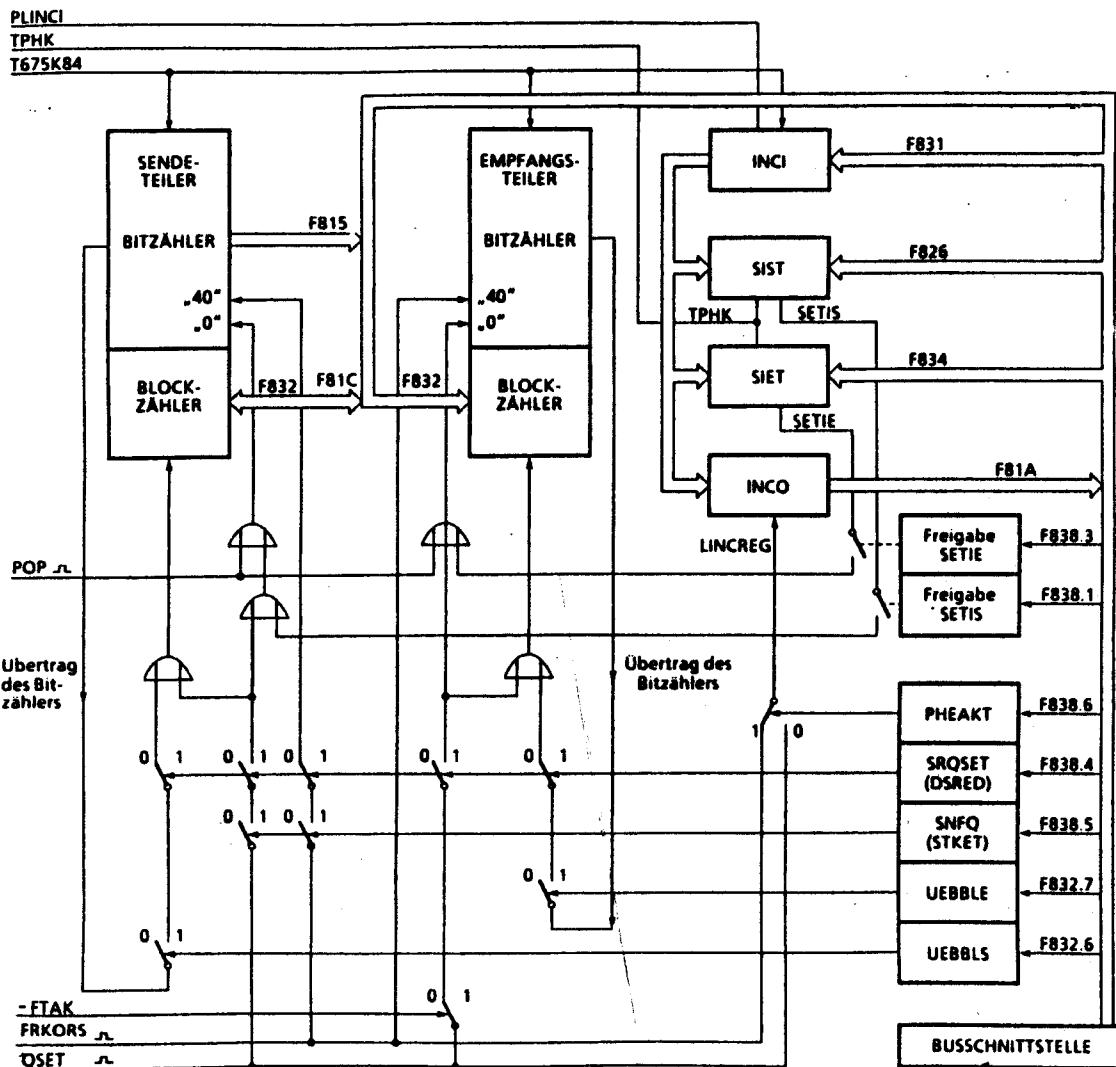

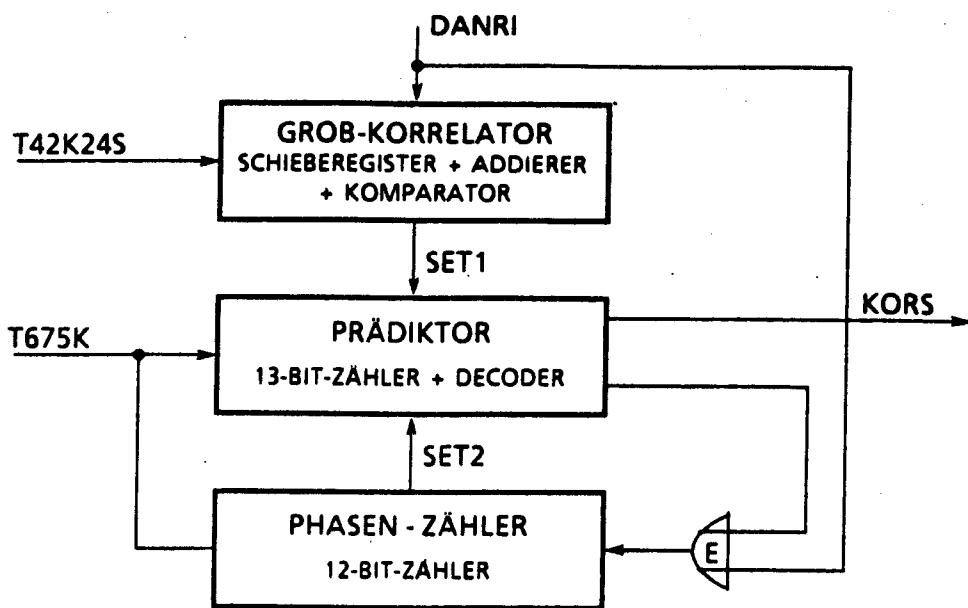

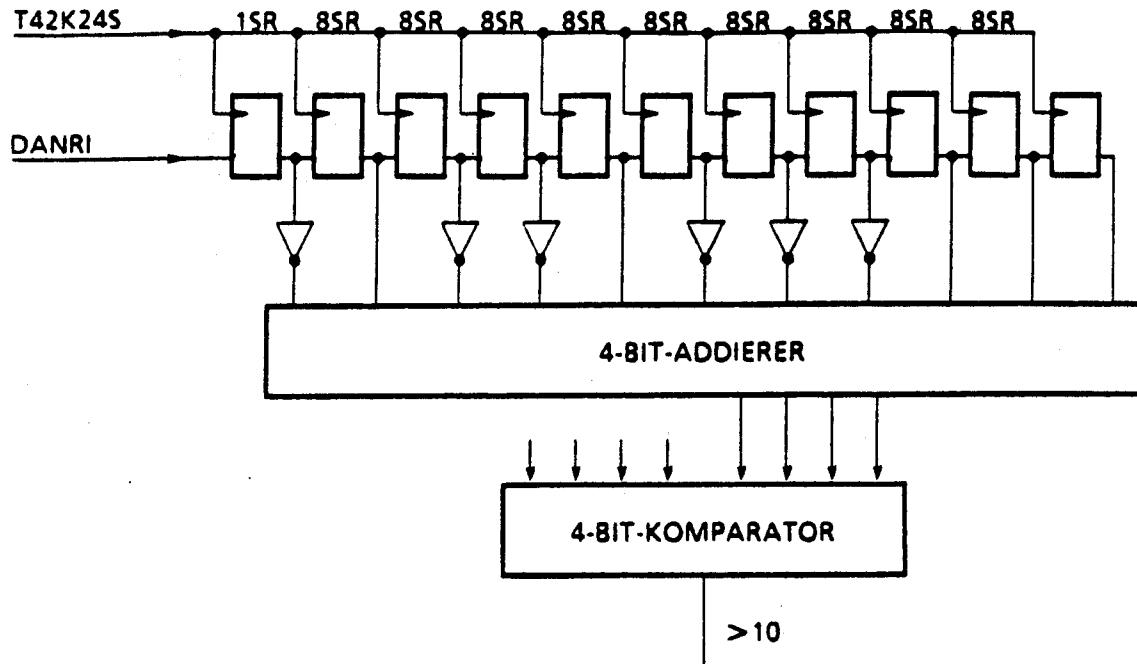

### 3.1.2 DKO-Zeitgeber S42024-H188-C1

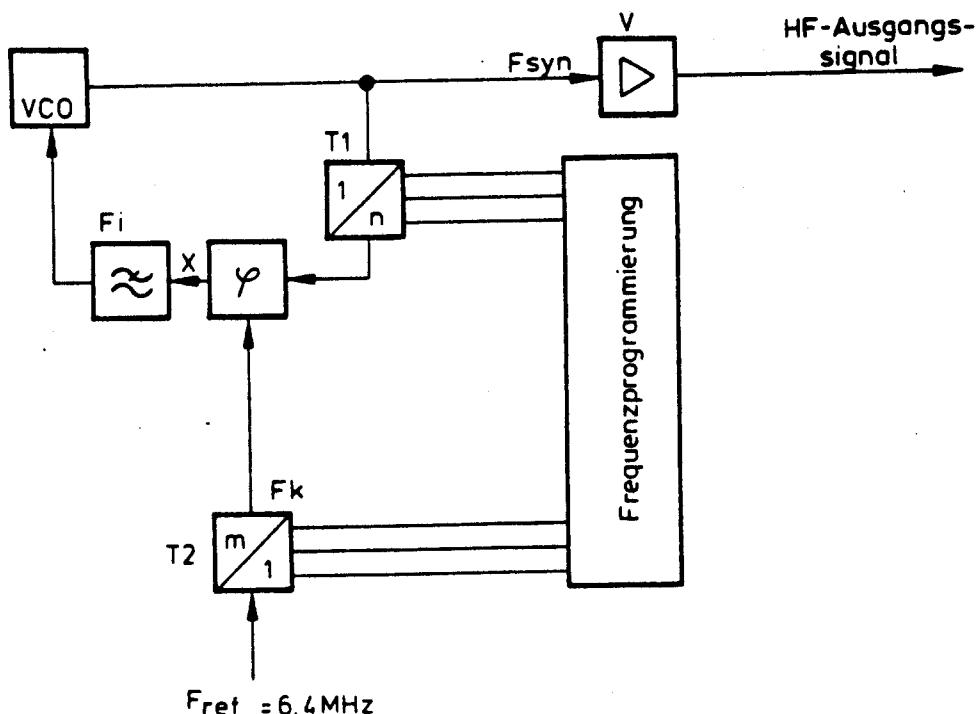

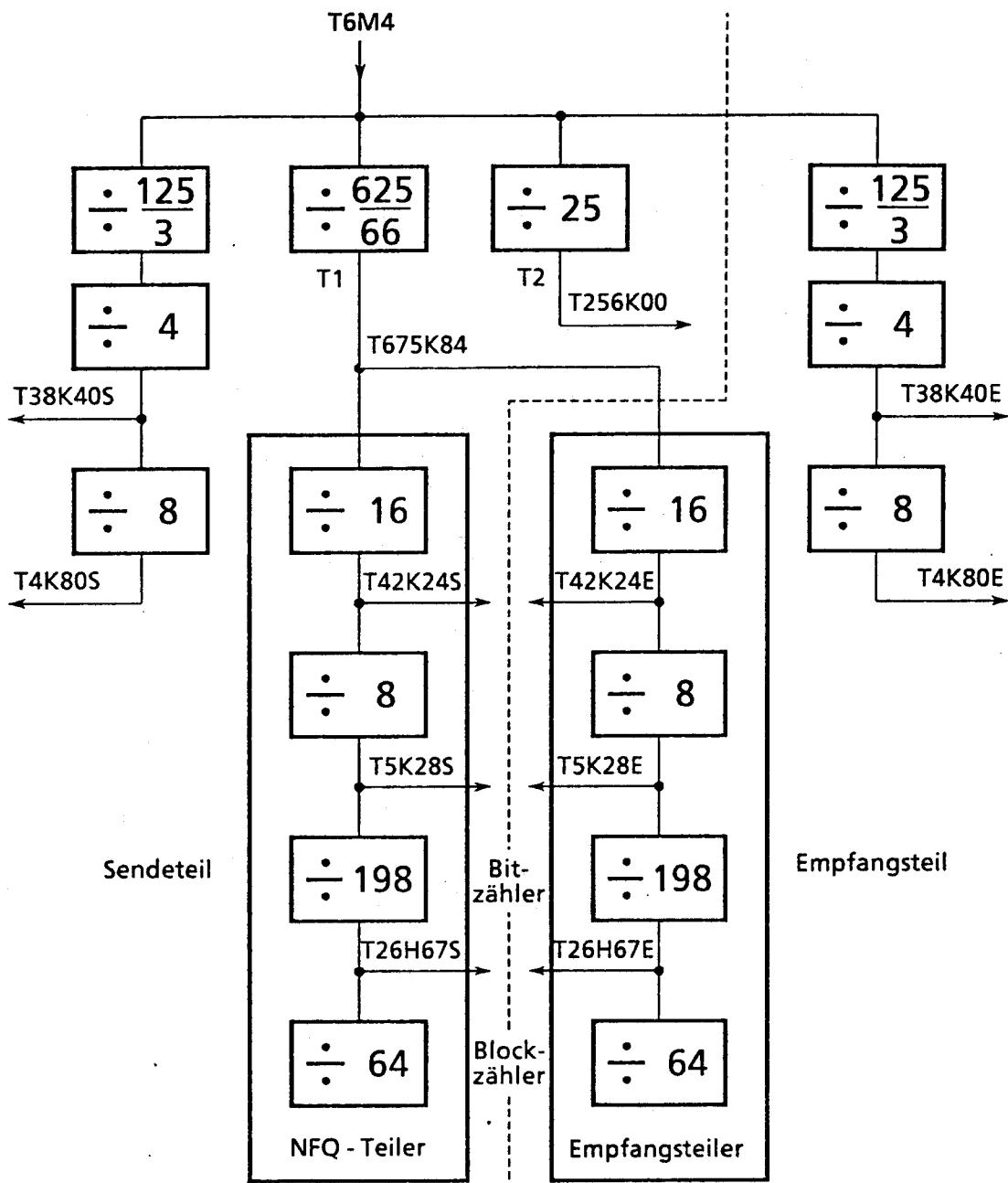

Der DKO-Zeitgeber besteht aus folgenden Baugruppen (siehe Bild 12):

- Taktzeugung T 256K

- Zeitgeber 0...2

- Überwachungstor- und Verzögerungslogik

- Adreßdecoder

- serielle Schnittstelle EPCI 2661

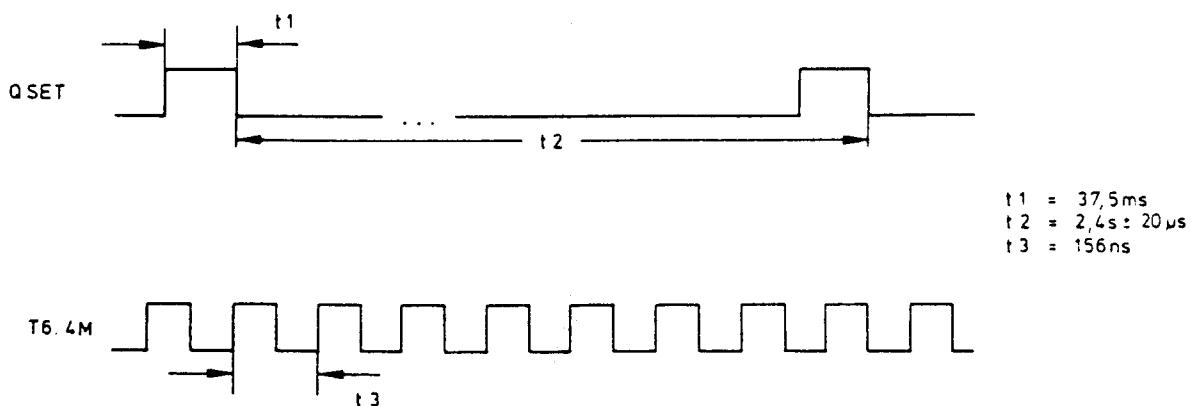

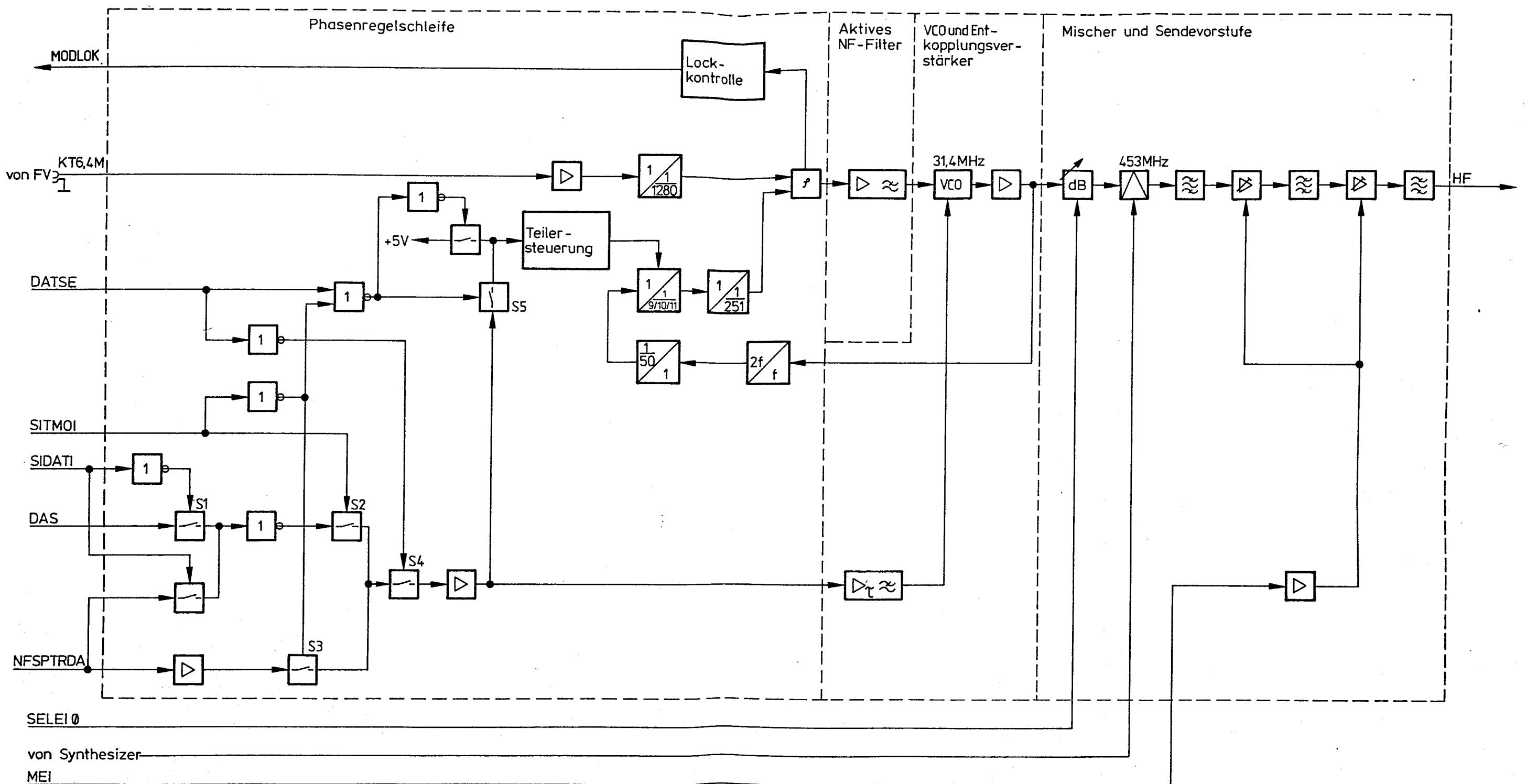

Der DKO-Zeitgeber erzeugt die für den Betrieb der FDS notwendigen Takte aus den zentralen Takten der Basisstation (EXE-6,4MHz, EXE-2,4S). Diese Signale werden im Phasenempfänger erzeugt und über den Frequenzverteiler dem DKO-Zeitgeber zugeführt. Das Rechtecksignal EXE-2,4S wird auf symmetrischen Leitungen, das sinusförmige Signal EXE-6,4 MHz auf einer Koaxialleitung übertragen. Ein Ausfall der Frequenzverteiler wird der Pegelüberwachung auf der Baugruppe Sicherheit FDS durch das Signal DKO-6,4M mitgeteilt. Bild 10 zeigt das Signalverhalten an der Takschnittstelle.

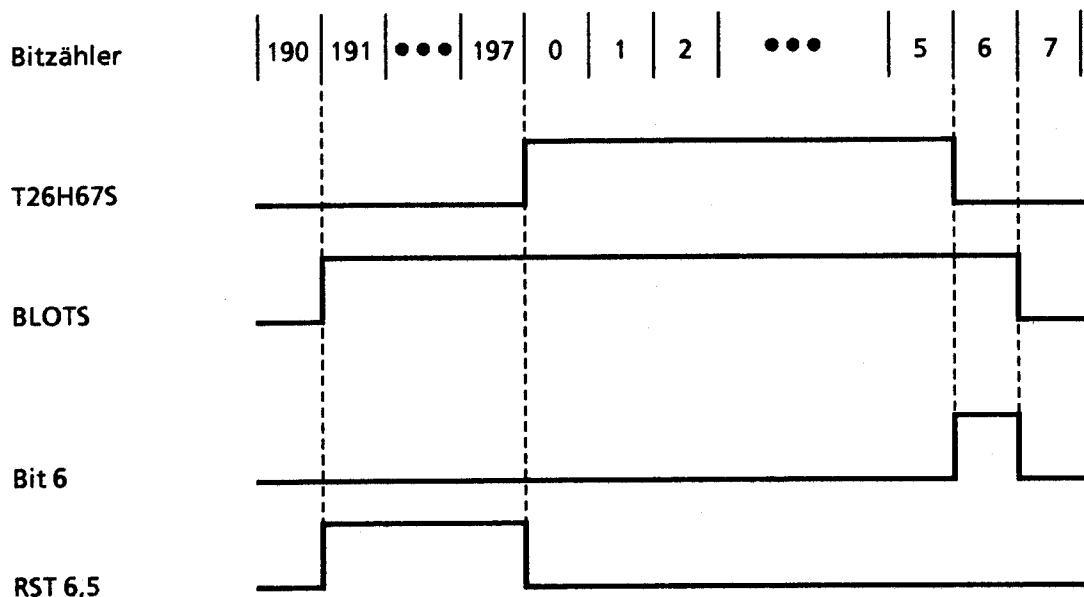

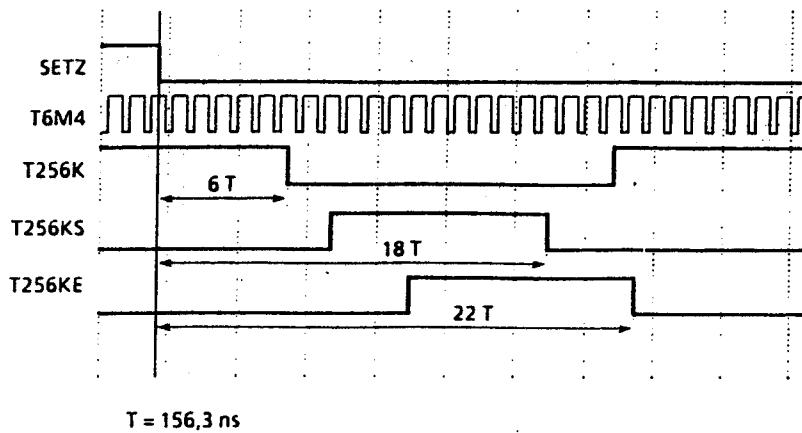

Bild 10 Signalverhalten an der Takschnittstelle

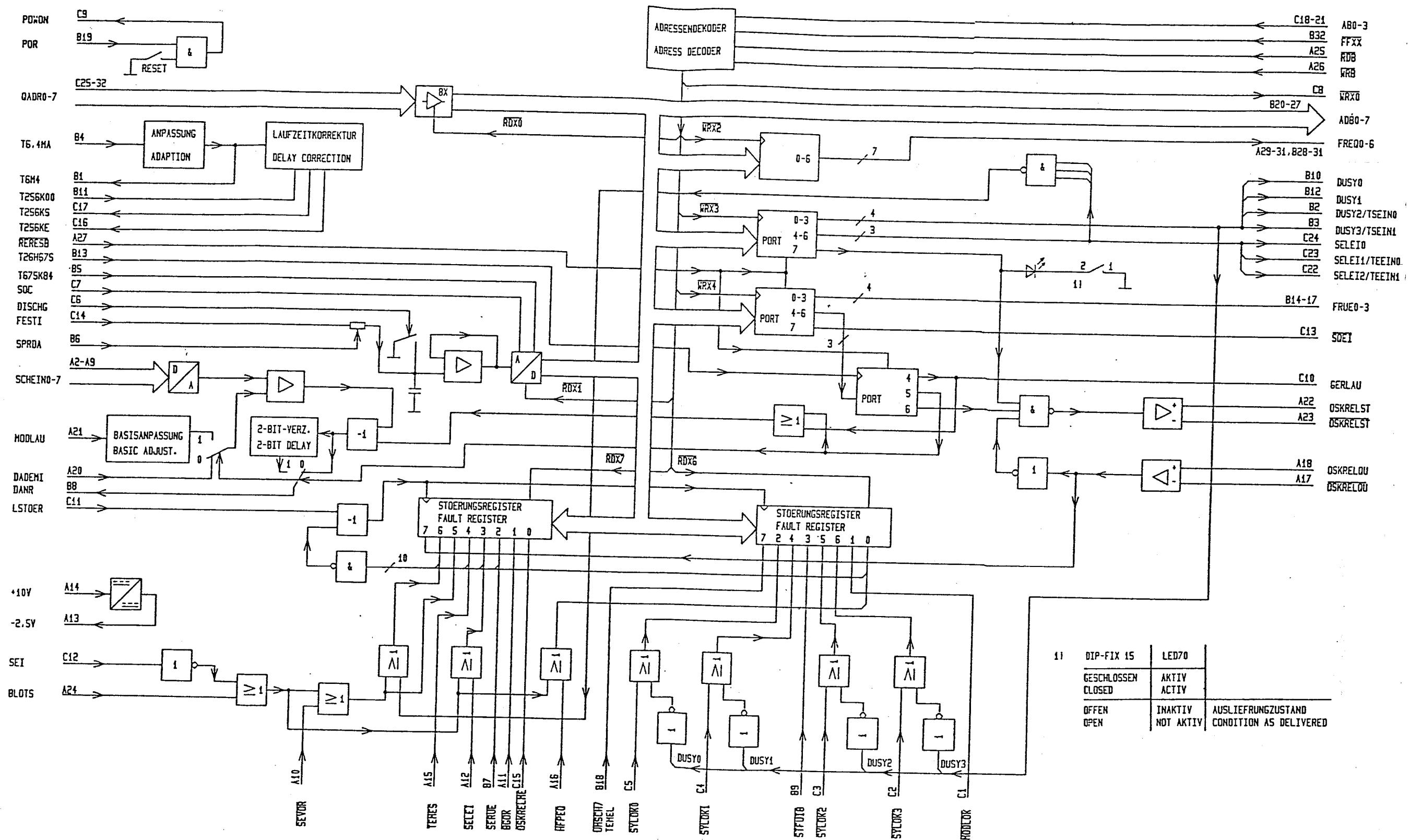

Bild 11 Übersichtsschaltplan DKo-Zeitgeber

Die programmierbaren Bausteine des DKo-Zeitgebers haben folgende Adressen:

Tabelle 7 I/O Adressen DKo-Zeitgeber

| Adressebereich | Speicher   | Funktionseinheit      |

|----------------|------------|-----------------------|

| 00H – 0FH      | USART 2661 | Ein/Ausgabe DKo ↔ FKS |

| 40H – 43H      | SAB 8254   | DKo – Zeitgeber 2     |

| 50H – 53H      | SAB 8254   | DKo – Zeitgeber 1     |

| 70H – 73H      | SAB 8254   | DKo – Zeitgeber 0     |

### 3.1.2.1 Takterzeugung T256K

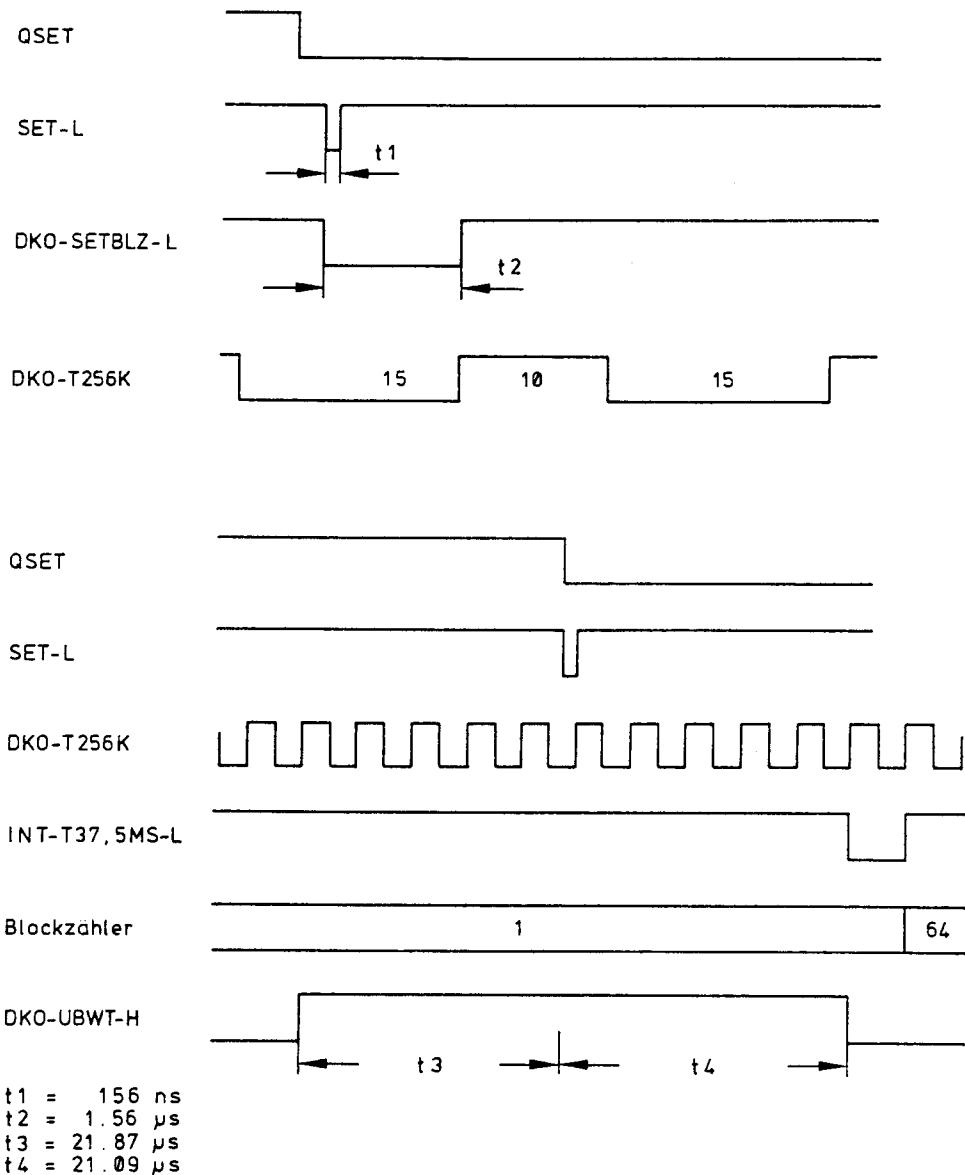

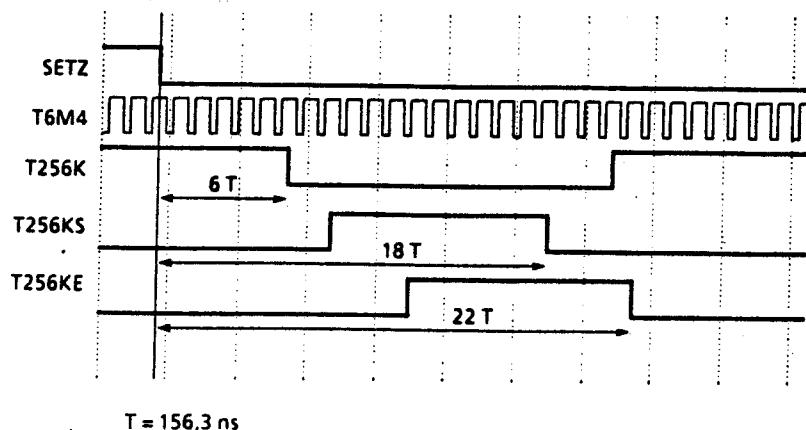

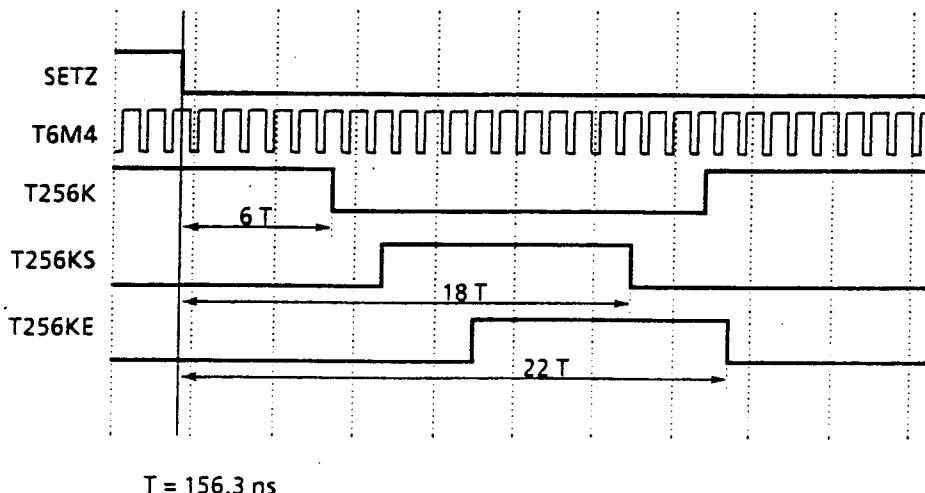

Der Takt T256K wird mit drei Schieberegistern und einem D-Flipflop erzeugt. Durch die drei 8-bit Schieberegister läßt sich die gewünschte Voreinstellung erzielen (Tastverhältnis 10 : 15). Als Clock dient der Takt T6,4M. Die Synchronisation zum Zeitzeichen wird dadurch erreicht, daß SET mit T6,4M gesteuert wird.

Unmittelbar nach dem Einschalten sind die Ausgänge der Zeitgeber undefiniert. Nach dem Eintrag in das Steuerwort-Register des Zeitgebers gehen die Ausgänge auf HIGH. Wenn alle drei Zähler des Zeitgebers 0 vollständig geladen sind (positive und negative Flanke an Takteingang der Zähler), beginnt der Zeitgeber 0 zu zählen. Bedingung für den Zählstart ist das erste Zeitzeichen. Die Rückflanke von QSET erzeugt die Synchronisation von QSET zu den Ausgängen der Zähler.

Mit Hilfe des Signals DKO-UBWT kann der DKV-Rechner feststellen, wann das erste Zeitzeichen SET, nach der Programmierung des Zeitgebers, im DKo aufgetreten ist. Nach diesem Zeitpunkt liefert der Zeitgeber die richtigen Takte. Nach dem nächsten SET wird die Fehlermeldung "Überwachung Zeitzeichen" zurückgesetzt und der DKV-Prozessor geht davon aus, daß die Teilerkette richtig läuft (2,4 Sekunden später muß die Überwachung der Teilerkette melden: Teilerkette läuft richtig).

Danach kann eine Fehlermeldung auftreten, wenn das DKO-SET ausfällt (Hardware-Defekt), oder der PHE umgeschaltet wird. Bei ordnungsgemäß arbeitenden Phasenempfängern kann bei einer betriebsmäßigen Umschaltung der Phasenempfänger ein DKO-SET-Signal ausfallen. Die DKO-SET Überwachung spricht aber erst an, wenn das Setzsignal DKO-SET zweimal hintereinander fehlt.

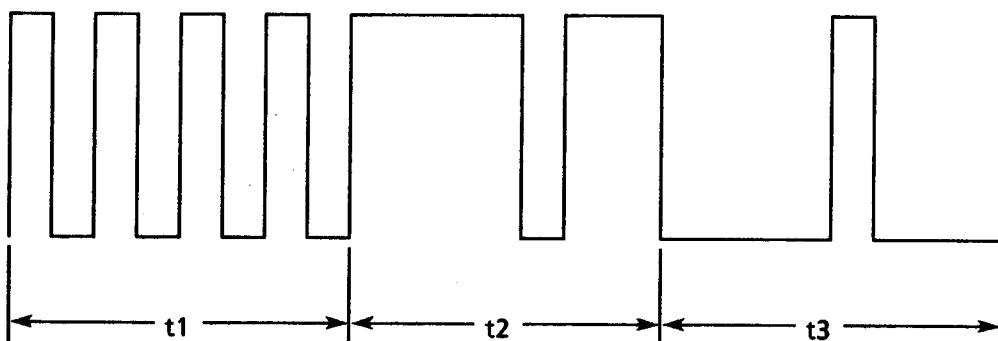

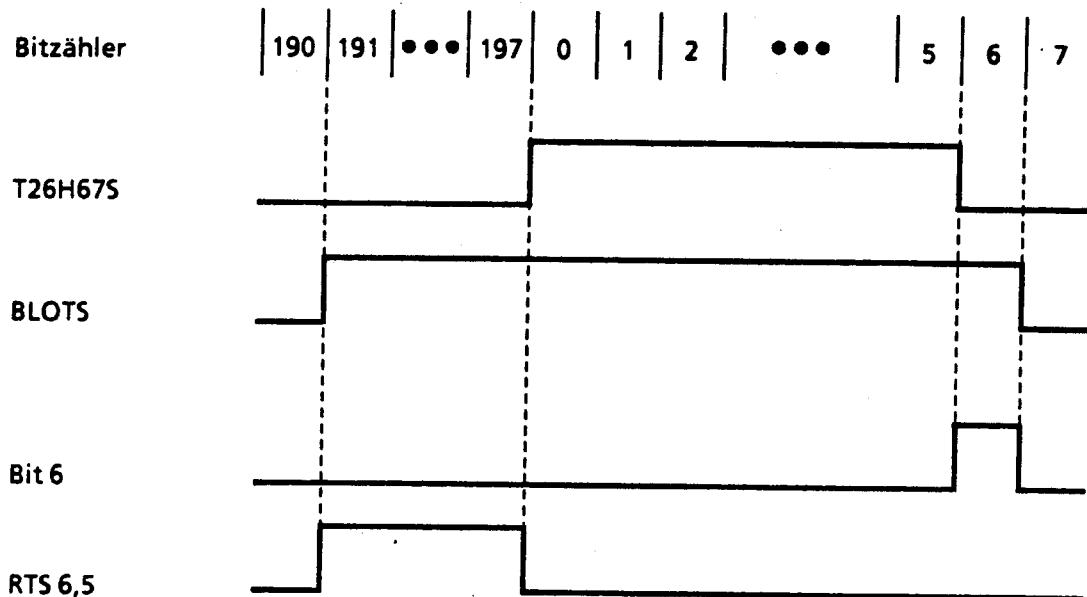

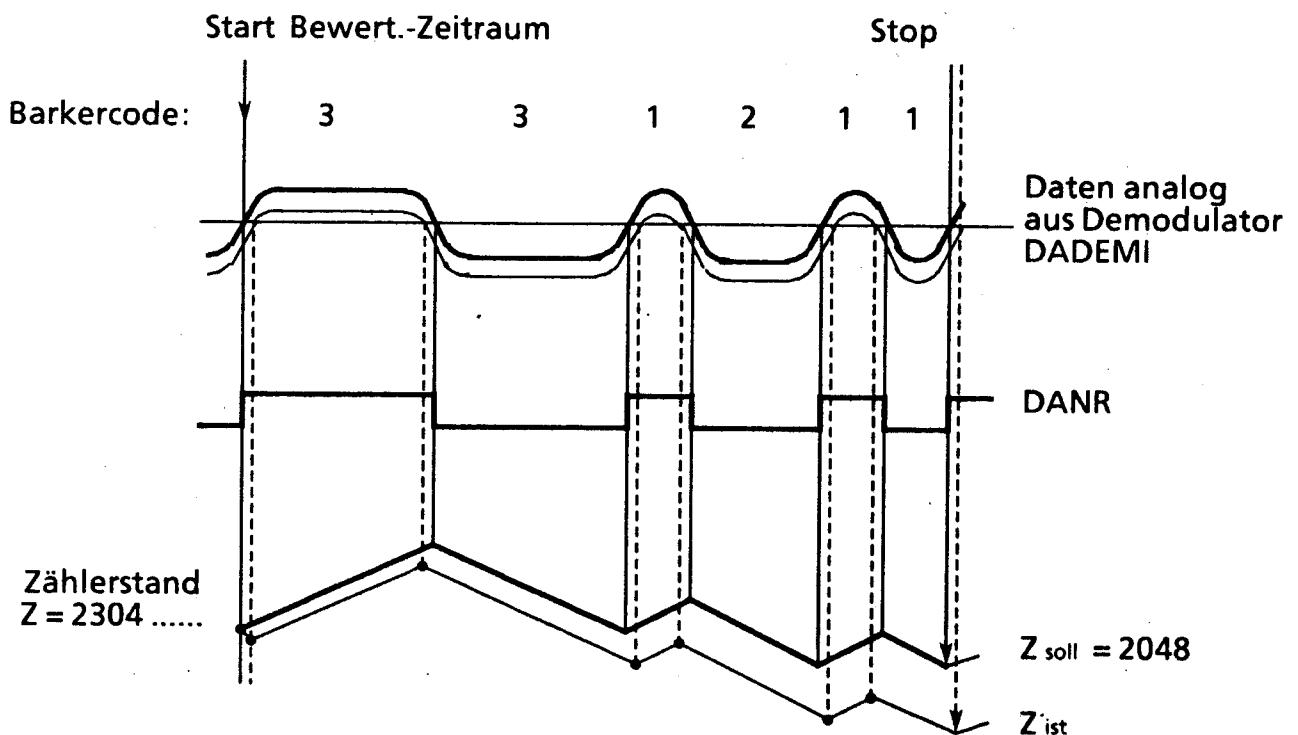

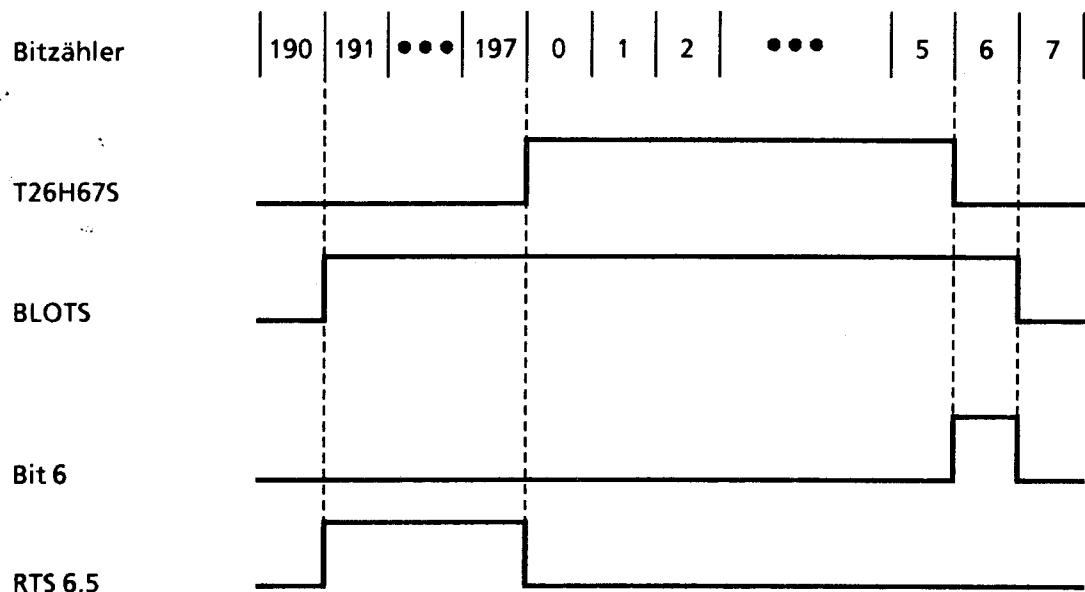

Bild 12 Zeitdiagramm des DKo-Zeitgebers

### **3.1.2.2 Zeitgeber 0**

Der Zeitgeber 0 (MD 8254) wird auf die Betriebsart 2 und duales Zählen eingestellt, in der die Zähler vom Anfangswert bis 1 abwärts zählen, bei Zählerstand 1 am Ausgang für eine Periode des Eingangstaktes auf LOW gehen, und dann, ohne neue geladen werden zu müssen, mit dem alten Anfangswert wieder zu zählen beginnen. Die Zähler sind mit folgenden Anfangswerten zu laden: Zähler 0 mit 9600, Zähler 1 mit 64, Zähler 2 mit 9587. Damit sind die Voraussetzungen gegeben, daß der Zeitgeber 0 die für den Betrieb der FDS richtigen Takte liefert.

Mit Hilfe des Zeitgebers 0 werden der Takt INT-T37,5MS-L, die Blockzählung und das Überwachungstor erzeugt.

#### **3.1.2.2.1 Takterzeugung INT-T37, 5MS-L**

Zähler 0 des Zeitgebers 0 teilt den Empfangstakt T256K durch 9587 auf einen 37,5-ms-Takt. Freigabe und Synchronisation des Taktes wird mit SET-L vorgenommen. INT-T37,5MS-L setzt die sechs Zähler der Zeitgeber 1 und 2 auf den vorher ins Zählerregister geladenen Wert.

Um einen Doppelimpuls bei positiver Korrektur des Signals SET-L um  $\pm 20 \mu\text{s}$  zu vermeiden, wird der Takt durch die Verzögerungsschaltung um  $21,09 \mu\text{s}$  verzögert.

#### **3.1.2.2.2 Blockzähler**

Der Blockzähler ist mit Zähler 1 des Zeitgebers 0 realisiert. Er wird mit den Anfangswert 64D geladen und durch INT-T37,5MS-L getaktet. Mit DKO-SETBLZ-L wird der Blockzähler im Zyklus von 2,4 s neu mit 64D geladen (siehe Bild 12).

Durch die Verzögerung von INT-T37,5MS-L um  $21,09 \mu\text{s}$  liegen Funkblocknummer und Blockzählerstand um  $25 \mu\text{s}$  auseinander.

#### **3.1.2.2.3 Überwachungstor**

Mit dem dritten Zähler des Zeitgebers 0 wird das Überwachungstor erzeugt. Zu Beginn des letzten Funkblockes (Blockzählerstand 1) geht der Blockzählerausgang auf LOW. Bei dieser Flanke beginnt Zähler 2 mit dem 256-kHz-Takt bis 9587 zu zählen. Mit dem Ausgangssignal wird ein JK-Flipflop (LS73) gesetzt, so daß das Signal DKO-UBWT-H auf den Zustand HIGH geht. Ohne Korrektur beträgt die Länge des Tors bis zum SET-L  $21,87 \mu\text{s}$ .

Die Rückflanke des Fensters wird von der Verzögerung des INT-T37,5MS-L-Taktes abgeleitet. Der Ausgang QE des Schieberegisters (LS164) geht auf den J-Eingang des JK-Flipflops. Die Zeitdauer von SET-L bis zur Rückflanke des Fensters beträgt  $(10*1/6,4 \text{ MHz} + 5*1/256 \text{ kHz}) = 21,09 \mu\text{s}$ .

Die Breite des Überwachungstores entspricht der maximalen Toleranz des Zeitzeichens QSET von  $\pm 20 \mu\text{s}$ . (siehe Bild 12).

Die FDS-Sicherheitstechnik vergleicht das Überwachungstor mit dem Zeitzeichen SET. Liegt das Zeitzeichen außerhalb des Überwachungstors ( $-21,87 \mu\text{s}$ ,  $+21,09 \mu\text{s}$ ), spricht der Fehlerdetektor an.

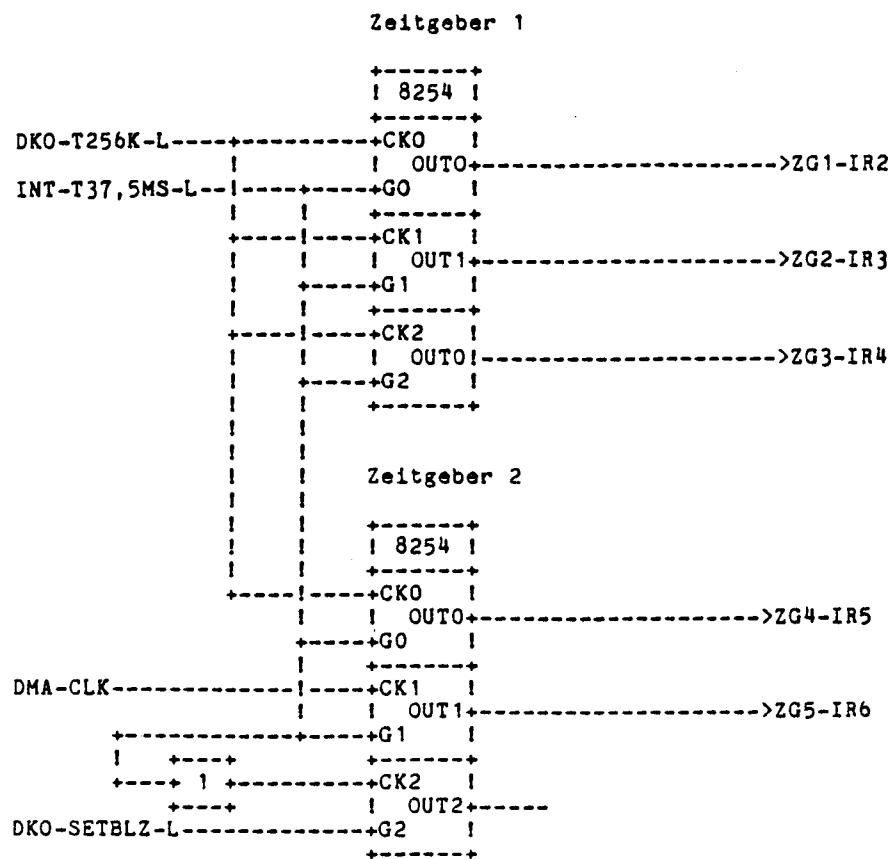

### 3.1.2.3 Zeitgeber 1, 2

Die Zeitgeber 1 und 2 stehen der Software für die Erzeugung eines Zeitrasters von 256 kHz zur Verfügung. Die von beiden Zeitgebern erzeugten Signale DKO-ZG1-L...6-L liegen im Takt INT-T37,5MS-L.

Tabelle 3 zeigt die Zuordnung der Zeitgeber-Interrupts zu den Eingängen des PIC.

Bild 13 Beschaltung Zeitgeber 1,2

### **3.1.2.4 Überwachungstor und Verzögerungslogik**

Überwachungstor und Verzögerungslogik werden vom Zeitgeber 0 sowie den Signalen SET-L und T256 kHz gesteuert. Die Funktion ist unter Pkt. 3.1.2.2 beschrieben.

### **3.1.2.5 Adreßdecoder**

Der Adreßdecoder ist mit dem Decoder LS 138 realisiert. Vom Adreßbus sind die Adreßbits A12...15 angeschlossen. Die Freigabe wird durch ZG-ADE-L vorgenommen.

Decodiert werden die CS-Signale für die Zeitgeber 1 und 2 (CS-TIMER1, CS-TIMER2) sowie den seriellen Schnittstellenbaustein ST 2661 (CS-USART).

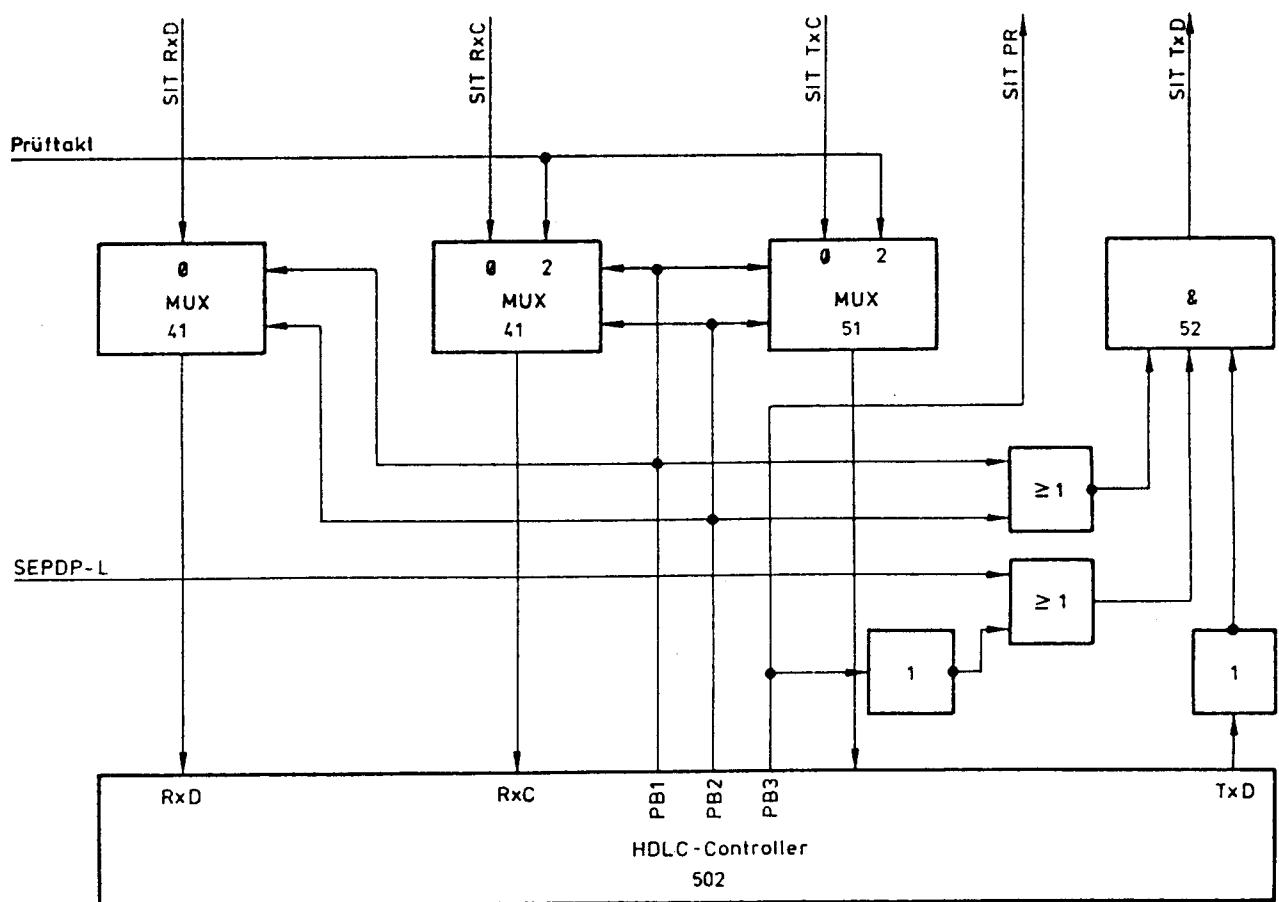

### **3.1.2.6 Serielle Schnittstelle USART 2661**

Die serielle Schnittstelle zur FKS1 oder FKS2 bildet der USART-Baustein ST 2661.

Er empfängt am Eingang RxD die über die Leitung DKO-EMP-AUS-L von der FKS gesendeten Daten. In gleicher Weise werden die Daten von TxD des USART über die Leitung DKO-SEN-EIN-L zur Funkperipherie gesendet. Sende- und Empfangstakt werden von Takt T256K des DKo-Zeitgebers gebildet.

Die seriell empfangenen Daten werden vom USART auf den DKo-Systembus gelegt. Der USART wird von CS-USART freigegeben und, entsprechend dem Zyklus, von ZG-RD-L und ZG-WR-L. Mit DIR-R/W wird am Eingang R/W die Datenrichtung bestimmt.

Die Programmierung der Mode1-, Mode2 und des Kommando-Registers ist aus dem Datenblatt zu ersehen. Über das Statusregister SR7 ist erkennbar, ob ein Break vorliegt, da SR7 den Pegel von -DSR invertiert anzeigt. Data Set Ready (-DRS) ist zu diesem Zweck mit RxD (Receive Data) verbunden. Ein Pull-Up-Widerstand verhindert, daß bei inaktiven Multiplexern ein Break im Statusregister SR7 angezeigt wird.

Der EPCI wird mit dem 256-kHz-Übertragungstakt (RxC, TxC) betrieben.

(Takt T256K siehe Kapitel 3.1.2.1).

Tabelle 8 Adressierung PCI 2661

| I/O-Adresse | Betriebszustand                           |

|-------------|-------------------------------------------|

| 00H R/W     | EPCI Daten-, Empfangs- oder Senderegister |

| 01H R       | Statusregister                            |

| 02H R/W     | Moderegister I und II                     |

| 03H R/W     | Commandregister                           |

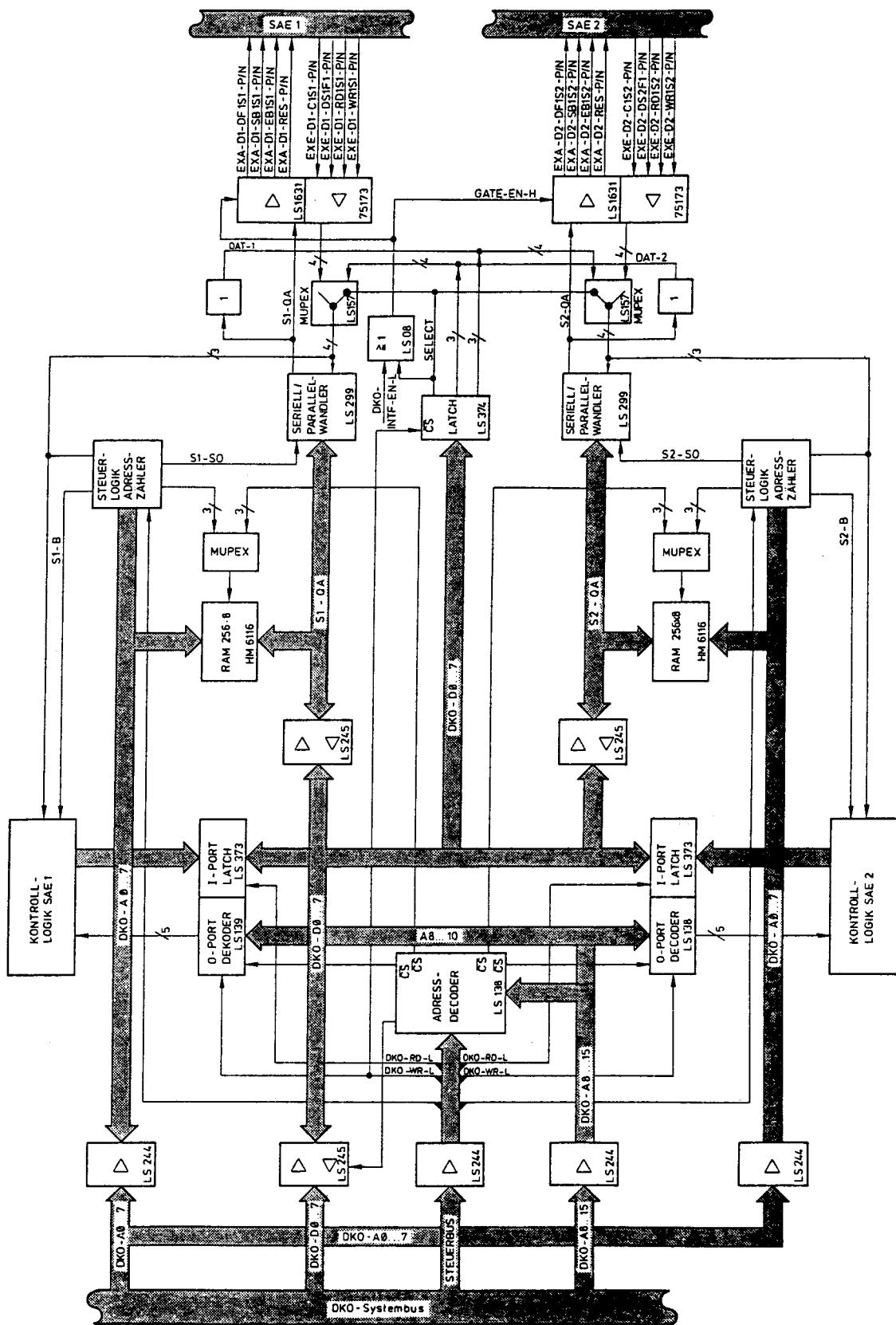

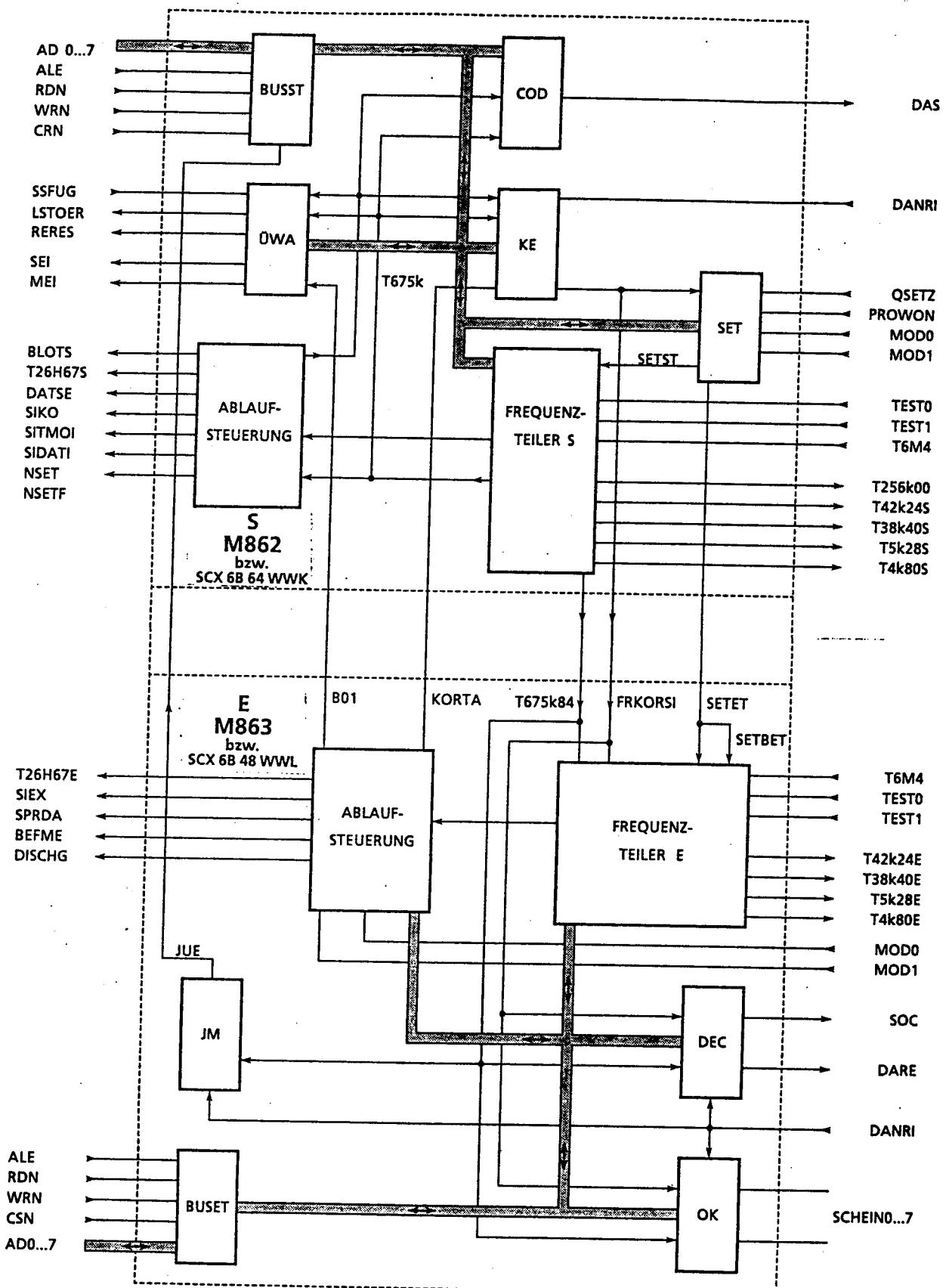

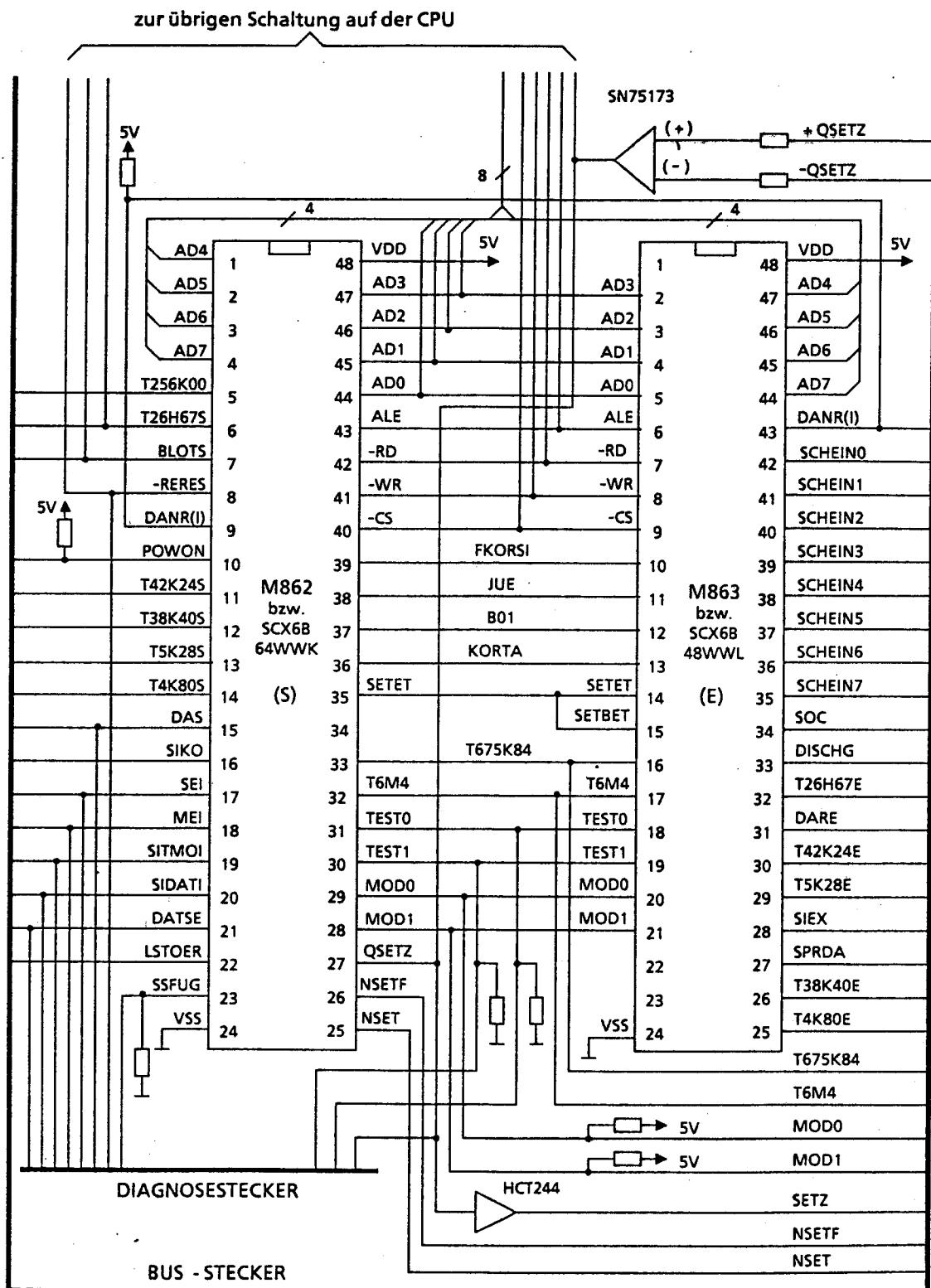

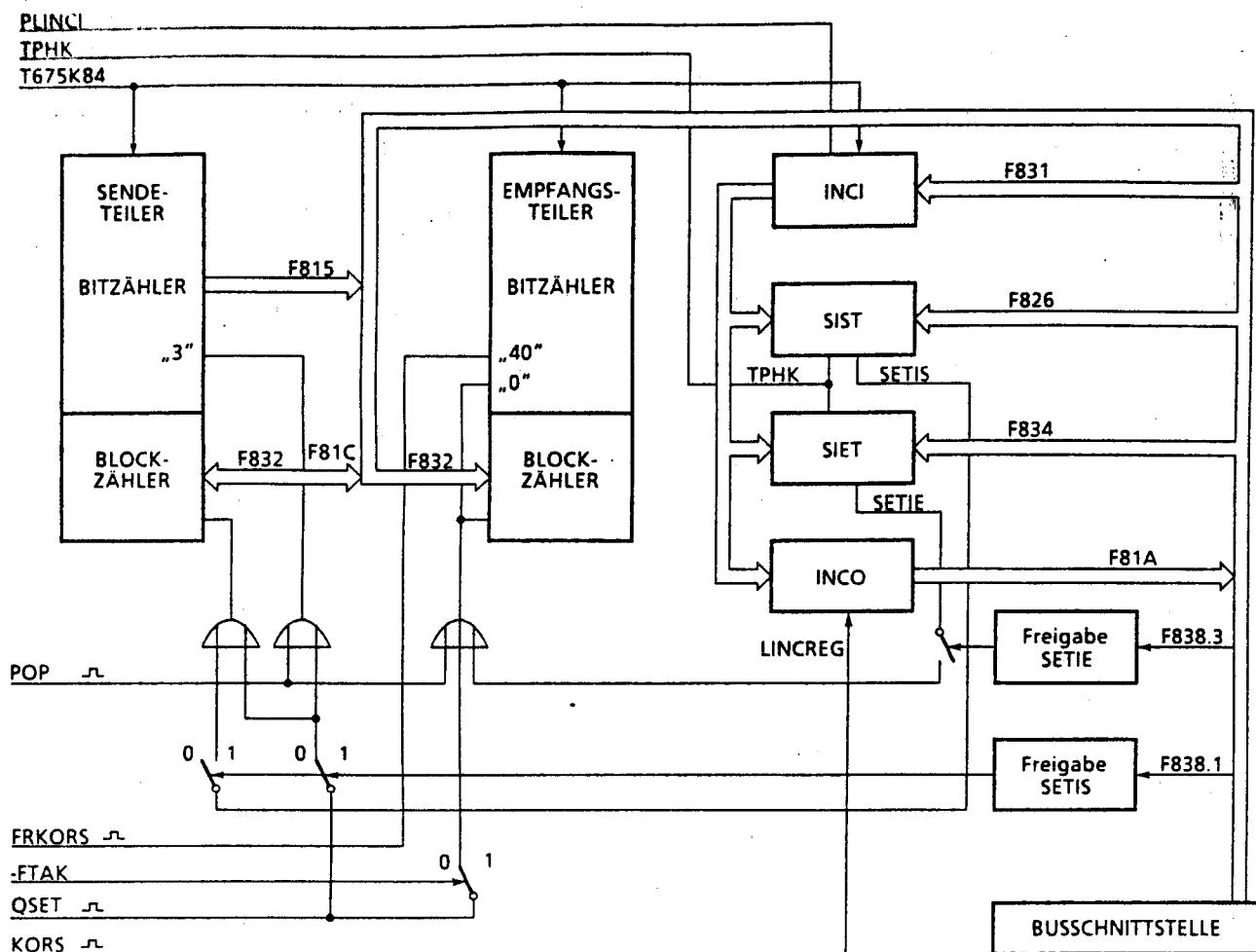

### 3.1.3 Schnittstelle ZZK S42024-H187-D1

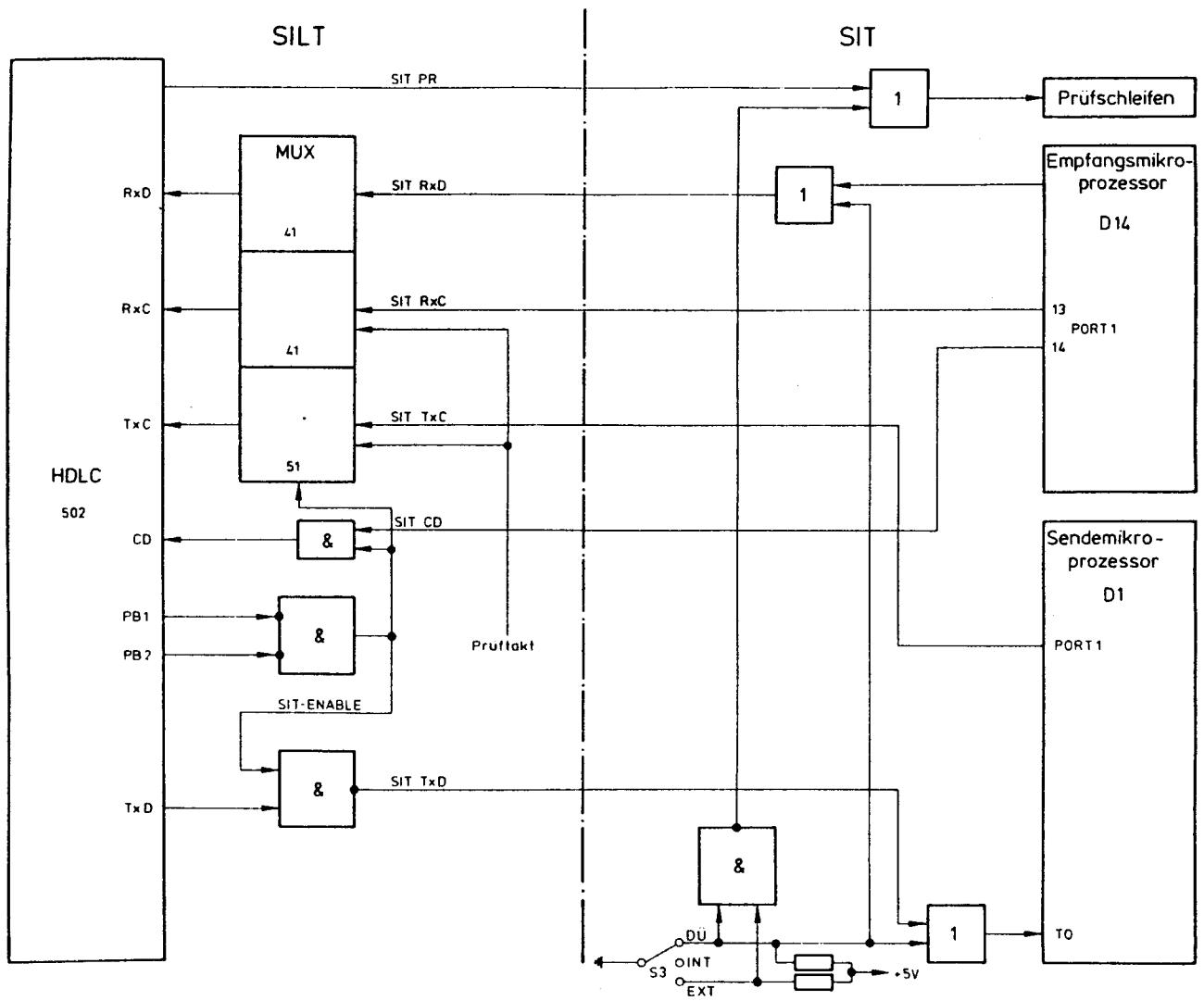

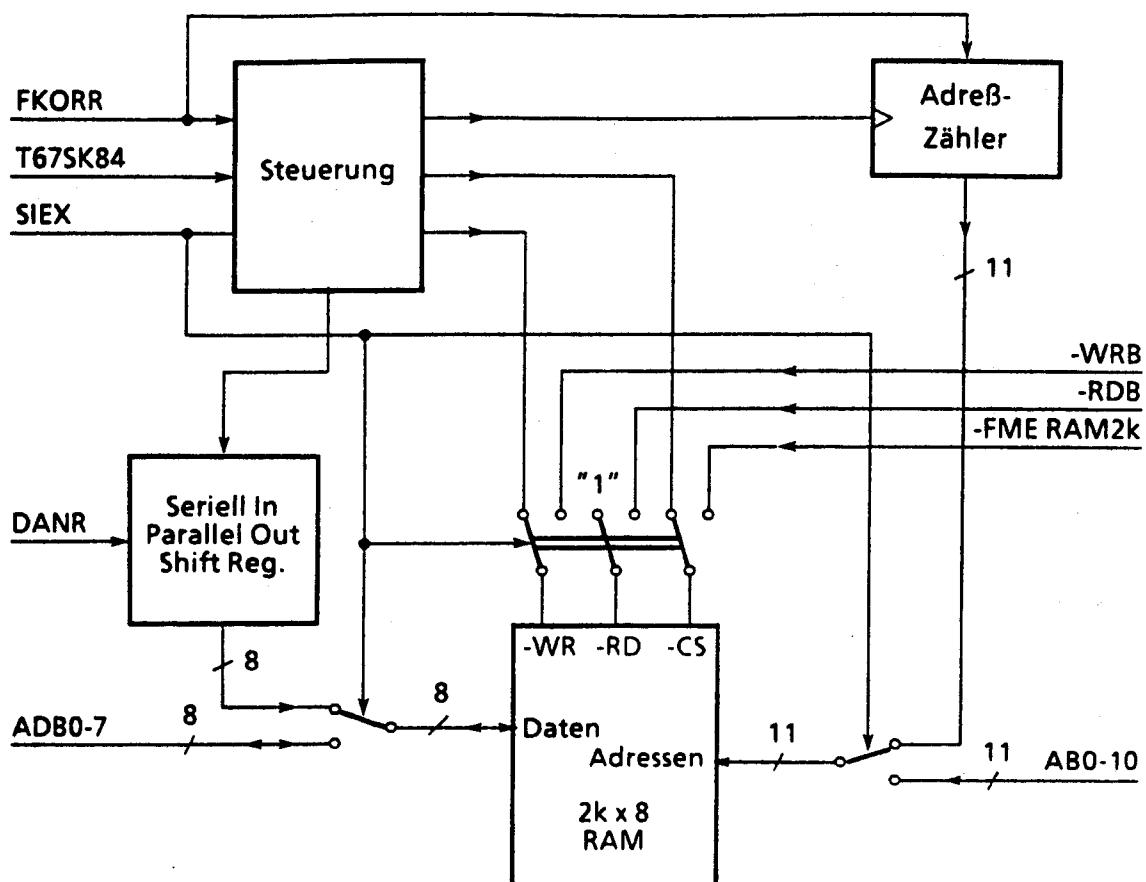

Die Schnittstelle ZZK besteht aus folgenden Funktionseinheiten (s. Bild 14):

- Steuerlogik

- Seriell/Parallel-Wandler

- Kontrolllogik

- Adreßdecoder

- Speicher

- I/O-Ports

- ZZK-Schleifentest.

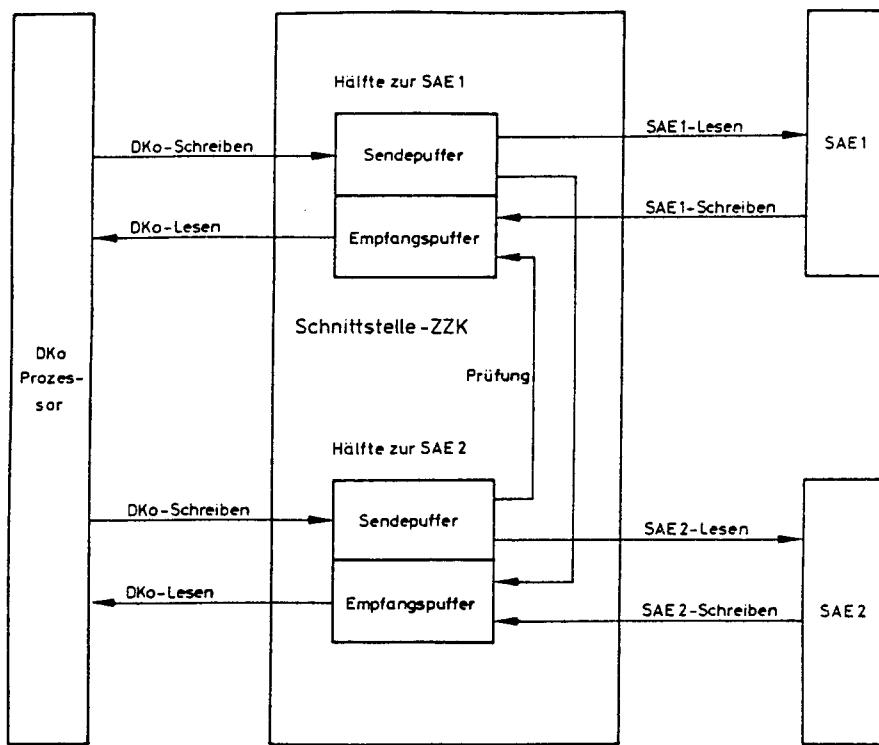

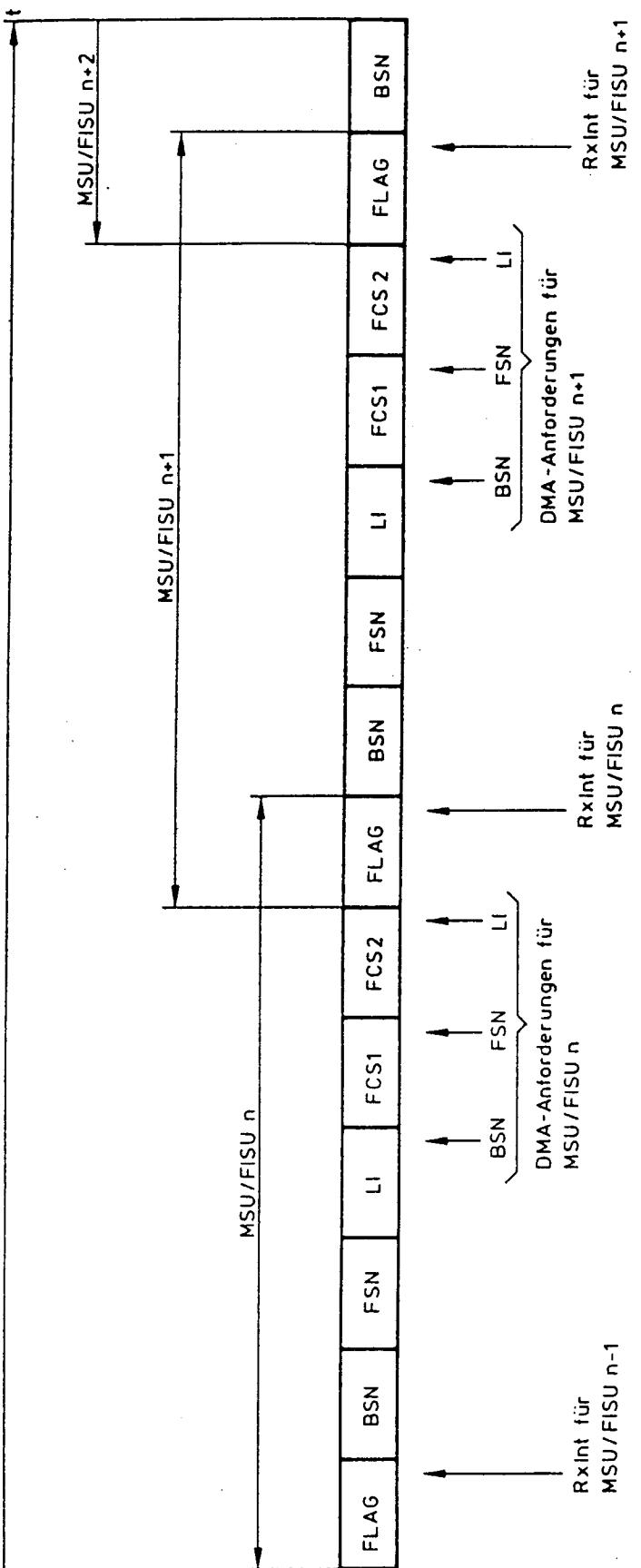

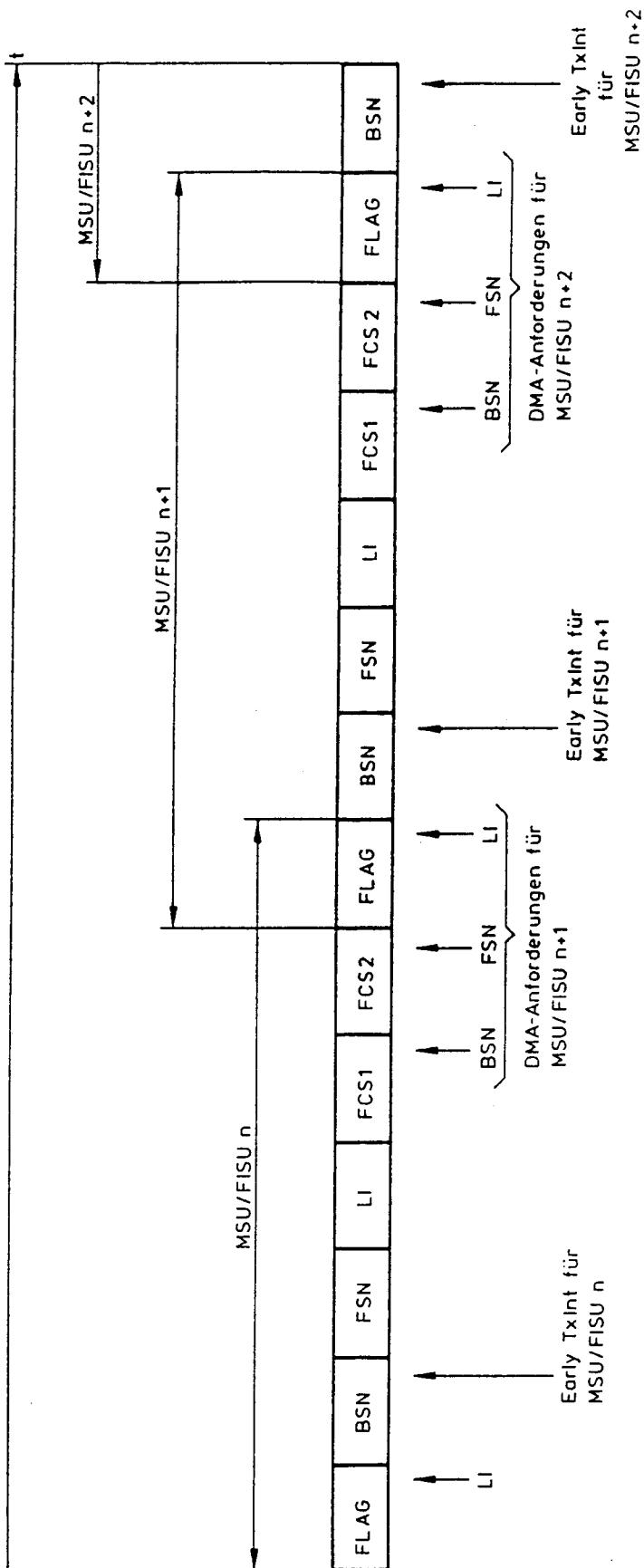

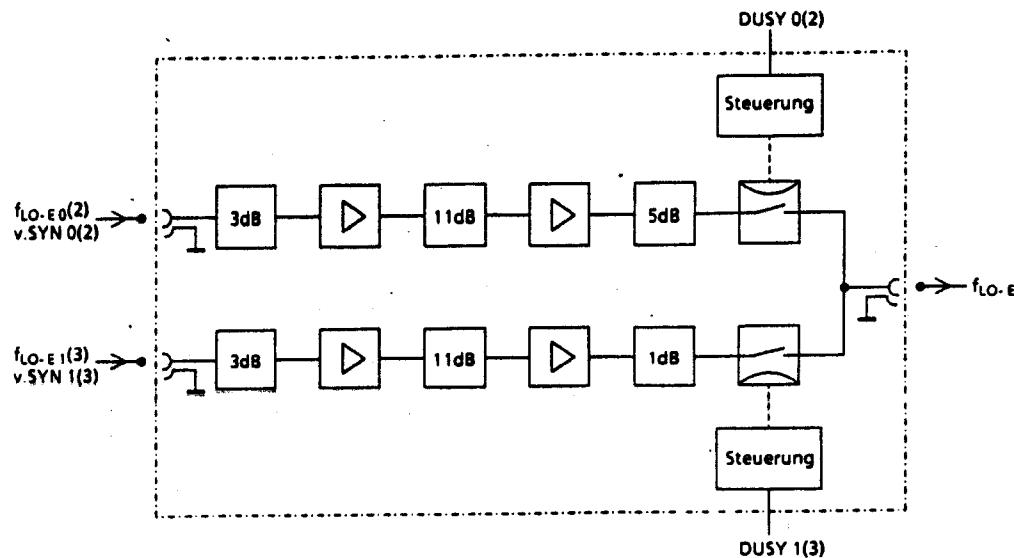

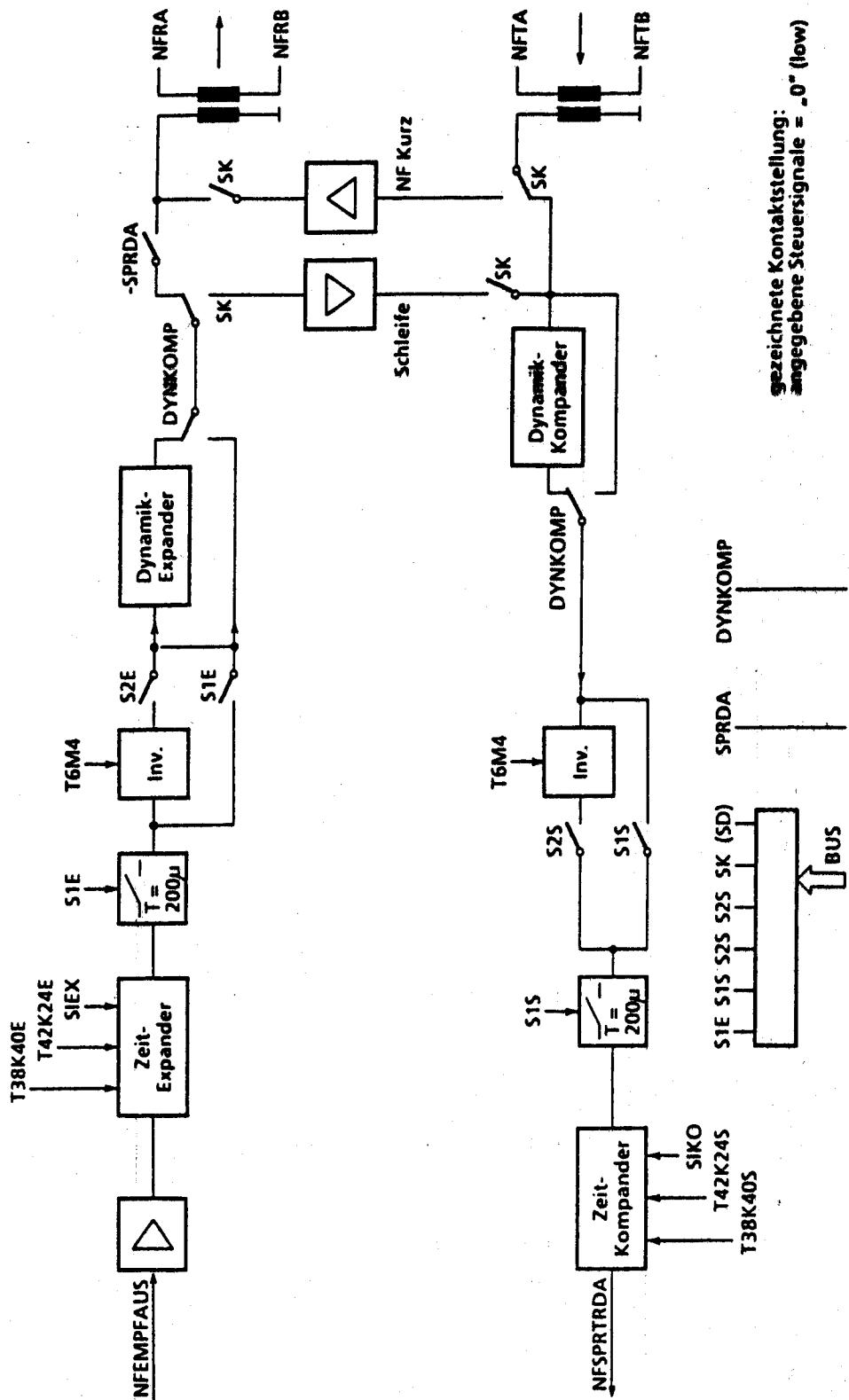

Um einen ausfallsicheren Betrieb zu gewährleisten, wird die Schnittstelle ZZK der FDS in zwei gleiche Hälften aufgeteilt und bildet so, mit einer passiven FDS, eine Datenverbindung zu den beiden SAE's. Ein 100%iger Betrieb, d.h. volle Datenübertragung ist nur mit beiden Hälften der Schnittstelle-ZZK möglich – die 2: FDS ist passiv, d.h. die Treiber sind hochohmig. Fällt ein Teil der Schnittstelle ZZK, oder eine SAE aus, steht noch die halbe Signalisierungskapazität zur Verfügung. Jede Hälfte der Schnittstelle ist einer bestimmten SAE zugeordnet. Von einer SAE aus betrachtet gehen die Daten parallel an beide Funkdatensteuerungen. Um den höchst möglichen Datendurchsatz zu erhalten, muß die Übertragung über beide Signalanpaßeinheiten stattfinden.

Der Transfer der Daten wird mit Handshake-Signalen geregelt. Die Handshake-Signale von der FDS an die SAE sind:

- SAE-SEBER Sender bereit

- SAE-EMBER Empfänger bereit.

Von der SAE aus wird eine Quittung über die Steuersignale vorgenommen:

- SAE-RD SAE liest

- SAE-WR SAE schreibt.

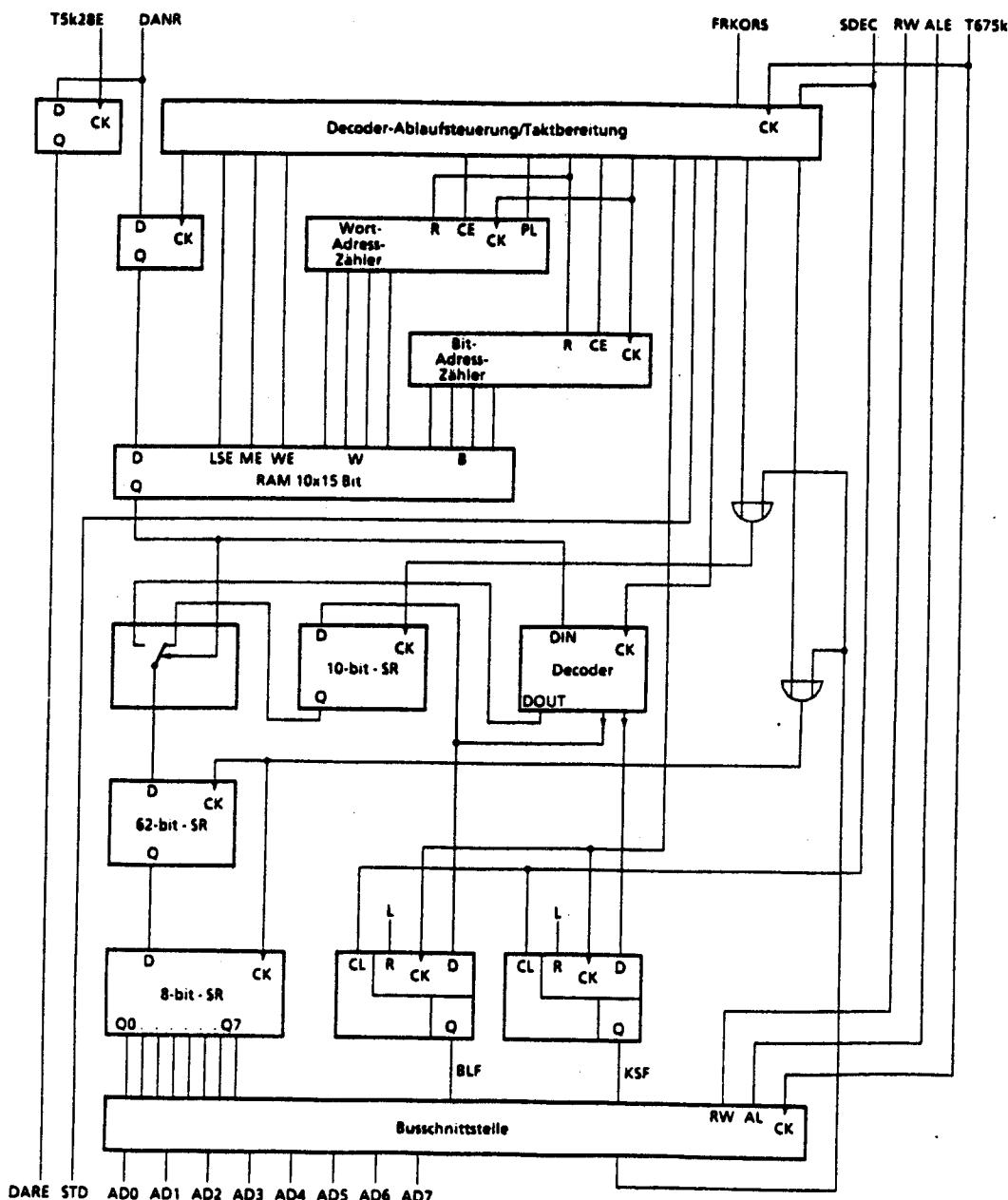

Bild 14 Übersichtsschaltplan Schnittstelle ZZK

Bei Spannungsausfall oder FDS-Einfachbestückung erkennt die jeweilige SAE die Signale EXA-DxSBxSx bzw. EXA-DxEIxSx und die Datenleitung EXA-DxDFxSx als HIGH (x = Nr. der jeweiligen SAE bzw. Schnittstelle ZZK).

### 3.1.3.1 Steuerlogik

Die Steuerlogik koordiniert die DKo- und SAE-Prozeduren. Sie steuert die Adressierung und stellt die sechs möglichen Betriebsweisen ein.

Folgende Betriebsweisen für jede der beiden Schnittstellenhälften sind möglich:

- DKo-Lesen

- DKo-Schreiben

- SAE (1 oder 2)-Lesen

- SAE (1 oder 2)-Schreiben

- Prüfung

- kein Datentransfer.

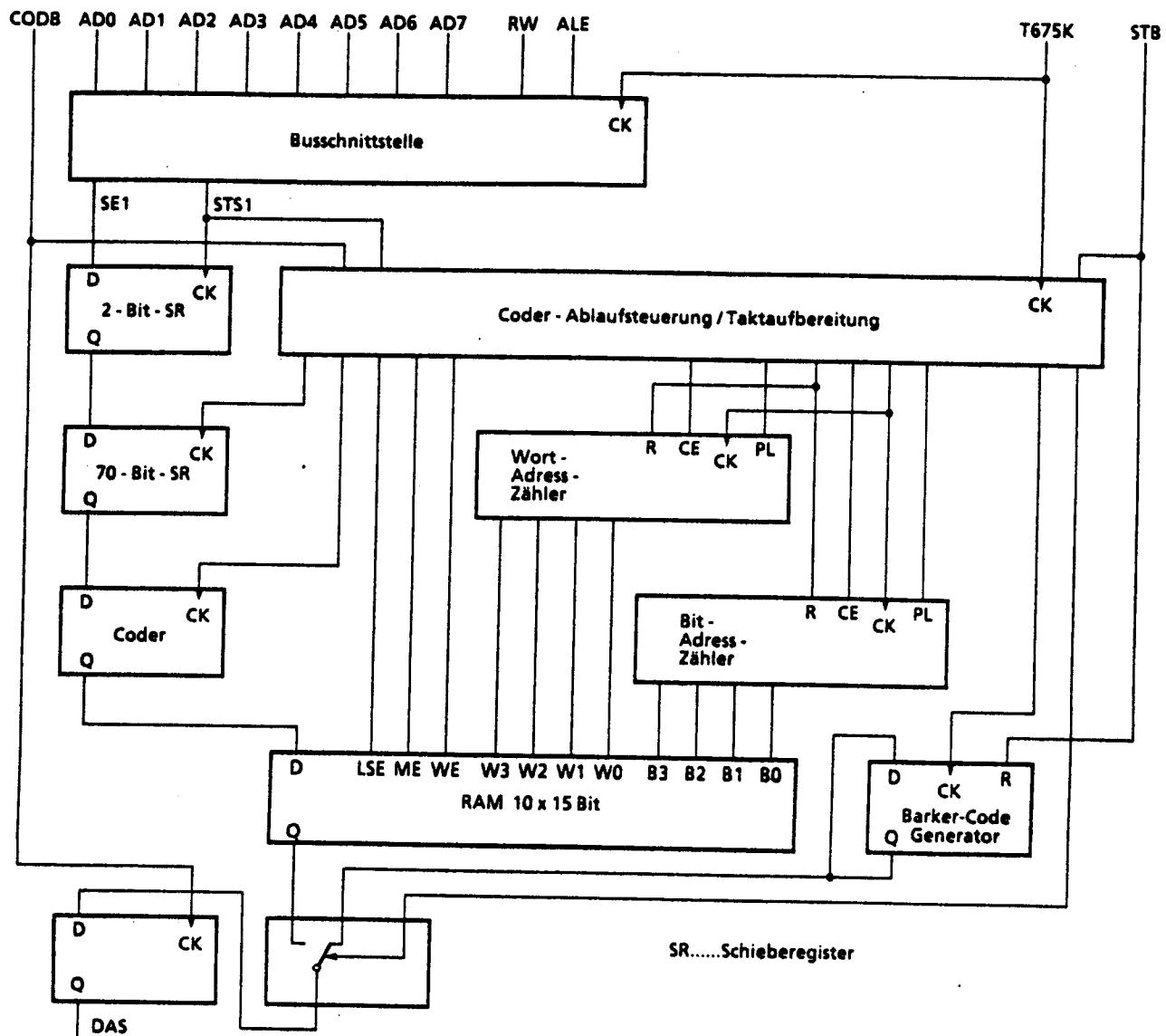

Bild 15 gibt einen Überblick über die Betriebsweise der Schnittstelle-ZZK.

Die Hälften der Schnittstelle ZZK können in folgender Weise parallel arbeiten:

- Parallel zur Betriebsweise DKo-Lesen bzw. DKo-Schreiben ist in der anderen Hälfte SAE-Lesen oder SAE-Schreiben möglich.

- Parallel zur Betriebsweise SAE-Lesen bzw. SAE-Schreiben ist in der anderen Hälfte jede Betriebsweise außer Prüfung möglich.

- Parallel zur Betriebsweise Prüfung ist keine andere Betriebsweise möglich.

Die I/O-Ports der Schnittstelle ZZK sind unabhängig von der Betriebsweise jederzeit ansprechbar.

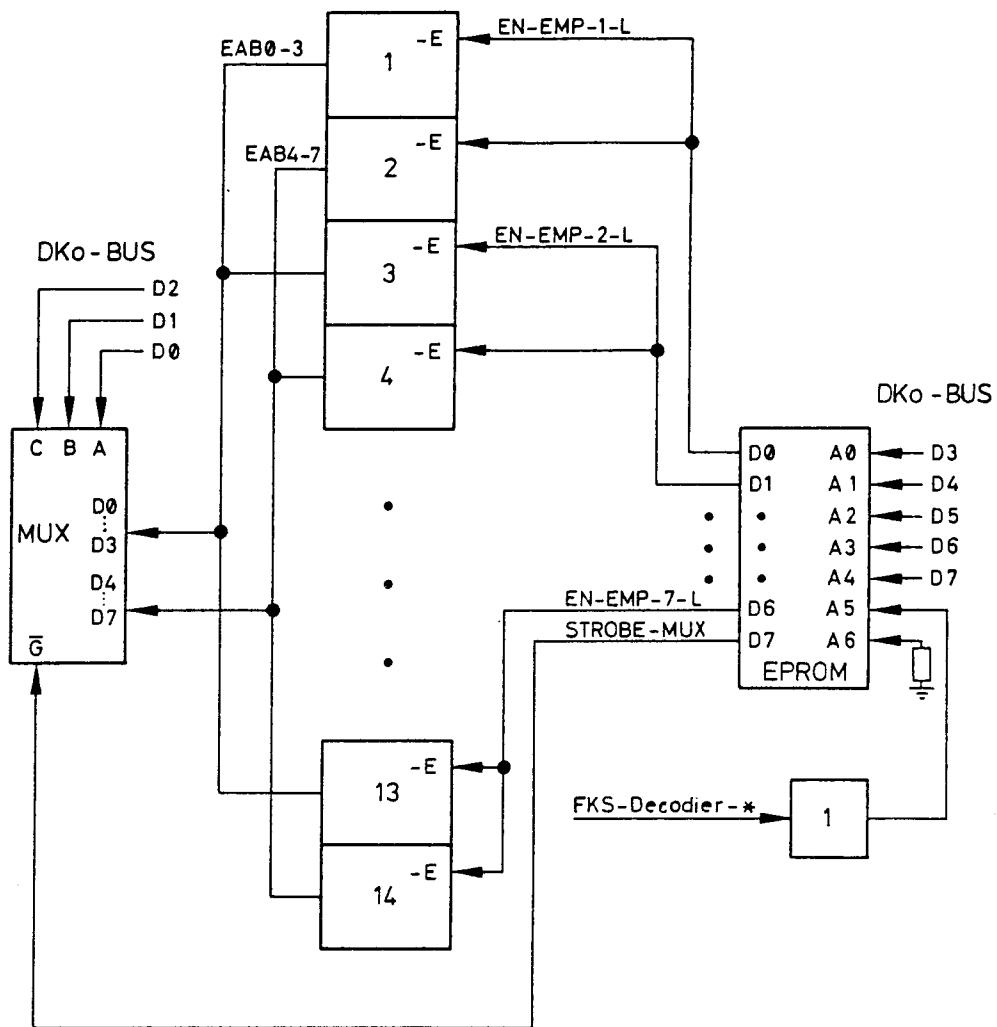

Der DKo-Prozessor kann abhängig von den Betriebsweisen über den DKo-Systembus direkt auf die beiden Pufferspeicher (HM 6116) der Schnittstelle zugreifen. Die Vergabe der Speicherbereiche für RAM SAE1 und RAM SAE2 ist in Pkt. 3.1.3.6 beschrieben.

Zur Steuerung der Speicheradressierung bei der Übertragung SAE → FDS sind programmierbare Adreßzähler eingesetzt. Mit jedem übertragenen Byte wird der Zählerstand um 1 vermindert. Bei Zählerstand Null wird der Datentransfer abgebrochen und das Signal S1-B (S2-B) an die Kontrollogik geliefert. Mit S1-LD (S2-LD) wird nach jedem Übertragungsvorgang (SAE-WR und SAE-RD = LOW) der Adreßzähler wieder auf den Zählerstand 21D gesetzt. Die Steuerlogik übernimmt dann die Umstellung der Adreß- und Datenbustreiber, da beide Busse als interne und externe Busse arbeiten und multiplex betrieben werden.

Bild 15 Betriebsweisen der Schnittstelle ZZK

### 3.1.3.2 Seriell-/Parallel-Wandler

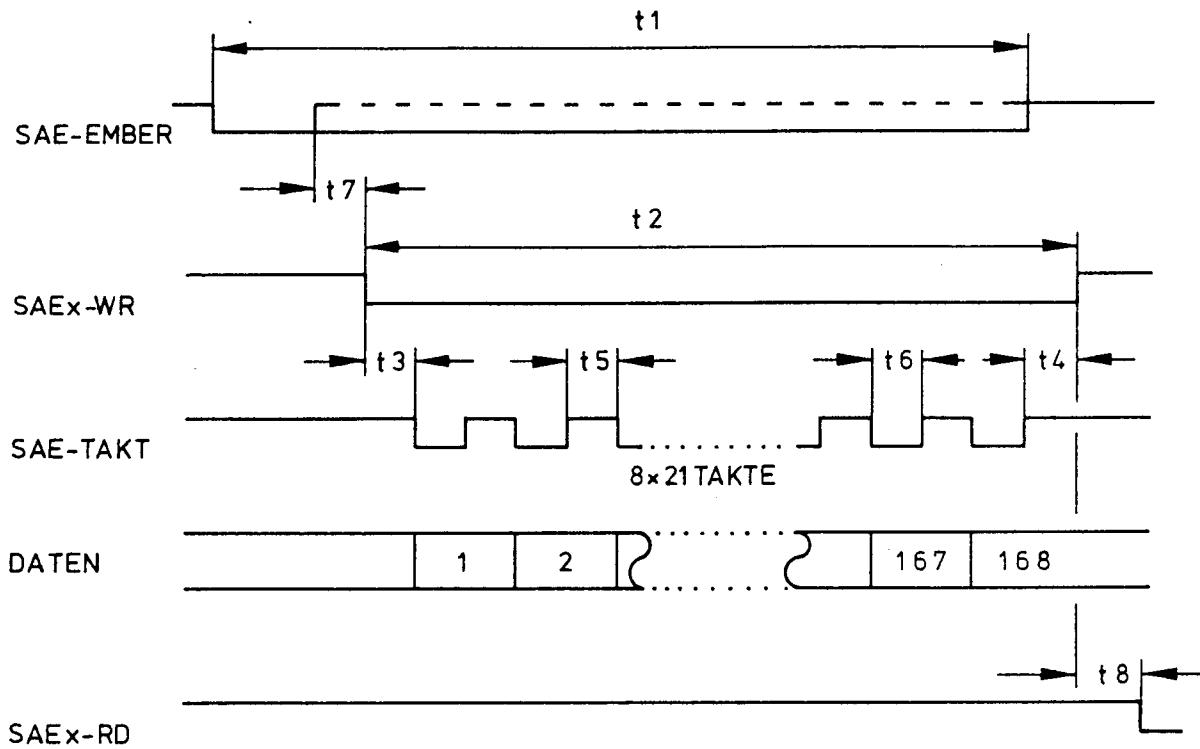

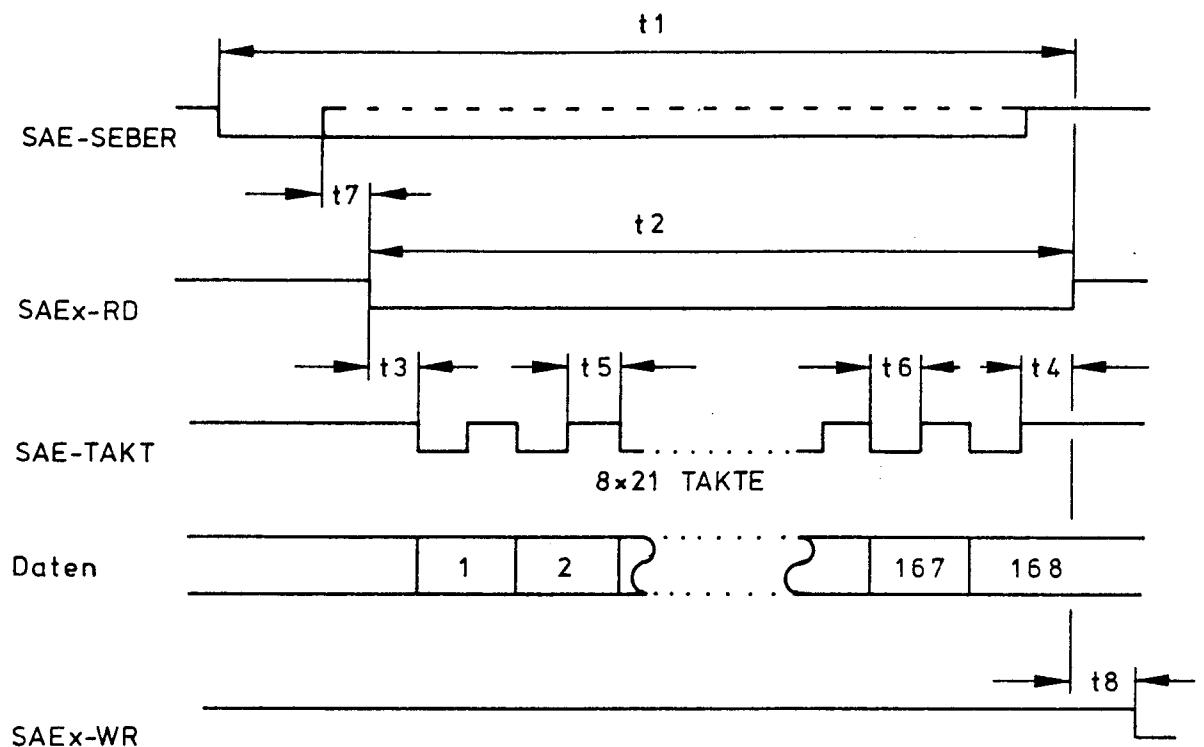

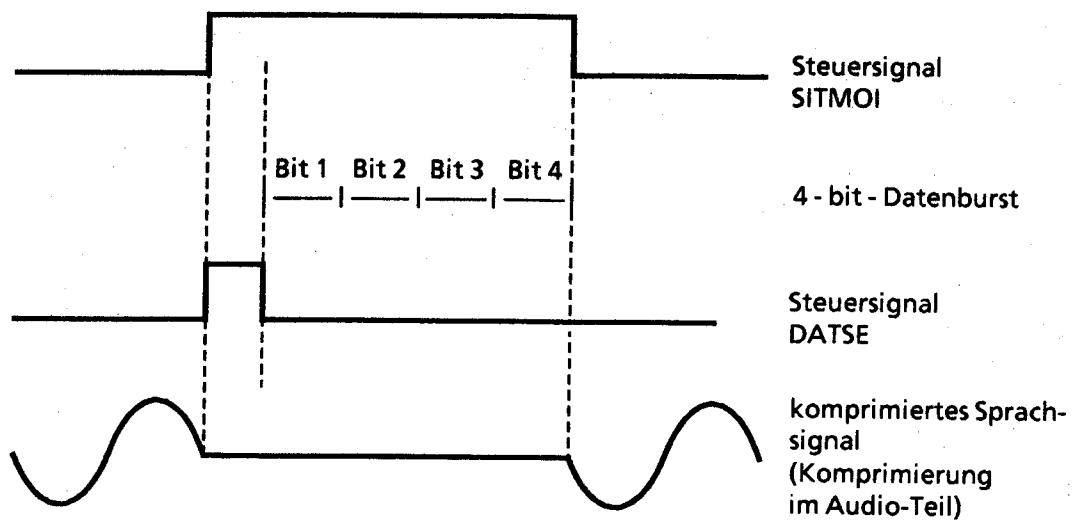

Die SAE beginnt den Datentransfer mit den Handshake-Signalen EXE-Dx-WRySx-L für das Schreiben bzw. EXE-Dx-RDySx-L für das Lesen. Schreibt die SAE über den Seriell-/Parallel-Wandler in den Pufferspeicher ein, so sendet sie 168 Takte ( $8 \times 21$ ) und gibt die Daten mit der negativen Taktflanke aus. Die Schnittstelle übernimmt die Daten mit der positiven Taktflanke. In Ruhestellung ist das Taktsignal HIGH. Liest nun die SAE über den Parallel-/Seriell-Wandler aus dem Pufferspeicher aus, so sendet sie ebenfalls 168 Takte.

Die Schnittstelle überlässt mit der negativen Taktflanke die Daten an die SAE. Mit der positiven Taktflanke übernimmt die SAE die Daten.

Damit Störimpulse auf der Takteleitung von der SAE zur Schnittstelle die Anfangsstellung der Adresszähler nicht verfälschen, wird die Anfangsstellung der Zähler geladen (S1-LD, S2-LD), wenn SAE-RD und SAE-WR nicht aktiv ist.

Liest oder beschreibt der DKo-Prozessor den Speicher, sind die Datenaus- bzw. Dateneingänge des Parallel-/Seriell-Wandlers im hohohmigen Zustand.

Die Signale S1-S0 bzw. S2-S0 bestimmen am Eingang S0 die Transferrichtung. Der Parallel-/Seriell-Wandler wird mit S1-CLOCK bzw. S2-CLOCK getaktet.

|    | MIN  | MAX    |

|----|------|--------|

| t1 |      | 20 ms  |

| t2 |      | 1,5 ms |

| t3 | 1 µs |        |

| t4 | 1 µs |        |

| t5 | 1 µs |        |

| t6 | 1 µs |        |

| t7 | 3 µs | 100 µs |

Bild 16 Übertragung SAE ↔ FDS

|       | MIN       | MAX         |

|-------|-----------|-------------|

| $t_1$ |           | 20 ms       |

| $t_2$ |           | 1,5 ms      |

| $t_3$ | 1 $\mu$ s |             |

| $t_4$ | 1 $\mu$ s |             |

| $t_5$ | 1 $\mu$ s |             |

| $t_6$ | 1 $\mu$ s |             |

| $t_7$ |           | 100 $\mu$ s |

| $t_8$ | 3 $\mu$ s |             |

Bild 17 Übertragung FDS  $\leftrightarrow$  SAE

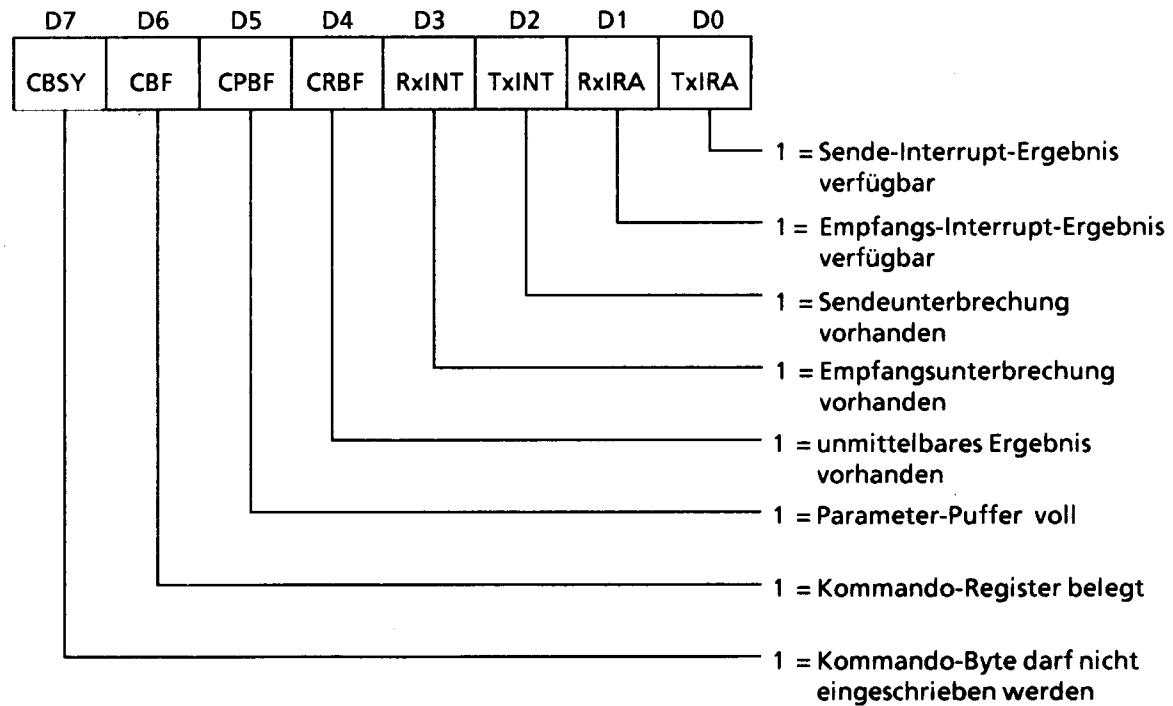

### 3.1.3.3 Kontrollogik

Mit der Kontrollogik überwacht der DKo-Prozessor die Betriebszustände der Schnittstelle ZZK. Über die I/O-Ports der Kontrollogik lassen sich unzulässige Betriebszustände, wie RAM überschreiben, RAM mehrfach lesen und Fehler in der Übertragung überwachen.

Der Zustand der Kontrollogik wird beeinflußt durch:

- die Signale der SAE

- Software-Eingriff über die Ports F0H bis F4H und E8H bis ECH (Betriebszustände)

- Signale des DKo-Prozessors (RESET)

- interne Abläufe (Signale der Steuerlogik).

Über die Output-Ports (OUTPUT S1, OUTPUT S2, 2 x LS138) ist mit Hilfe eines Befehls die Einstellung der unterschiedlichen Betriebszustände möglich.

Tabelle 9 Output-Port SAE1

| Adresse | Signalname   | Betriebszustand                              |

|---------|--------------|----------------------------------------------|

| F0      | S1-RESET     | Reset der Kontrollogik in den Anfangszustand |

| F1      | S1-SET-TFULL | Sende-RAM ist auf Zustand "voll" gesetzt     |

| F2      | S1-SET-REMPI | Empfangs-RAM ist auf Zustand "leer" gesetzt  |

| F3      | S1-FREIGABE  | Freigeben der Schnittstelle zur SAE1         |

| F4      | S1-SPERRE    | Sperren der Schnittstelle zur SAE1           |

Tabelle 10 Output-Port SAE2

| Adresse | Signalname   | Betriebszustand                              |

|---------|--------------|----------------------------------------------|

| E8      | S2-RESET     | Reset der Kontrollogik in den Anfangszustand |

| E9      | S2-SET-TFULL | Sende-RAM ist auf Zustand "voll" gesetzt     |

| EA      | S2-SET-REMPI | Empfangs-RAM ist auf Zustand "leer" gesetzt  |

| EB      | S2-FREIGABE  | Freigeben der Schnittstelle SAE2             |

| EC      | S2-SPERRE    | Sperren der Schnittstelle zur SAE2           |

Auskunft über die Betriebszustände und Betriebsweisen der Schnittstelle ZZK wird über die Input-Ports (INPUT S1, INPUT S2, 2 x LS373) erteilt.

Input-Port S1 (Adresse FAH) liefert das Statuswort ZZK-RDI1 von der Kontrolllogik SAE1.

Input-Port S2 (Adresse F8H) liefert das Statuswort ZZK-RDI2 von der Kontrolllogik SAE2.

Tabelle 11 Statuswort ZZK-RD/1

| Bit | Betriebszustand     | Funktion                     |

|-----|---------------------|------------------------------|

| 0   | SAE1-LESEVERSUCH    | Lesevorgang gestartet        |

| 1   | SAE1-TEMPTY         | Sende-RAM SAE1 leer          |

| 2   | SAE1-RD             | SAE1 Lesen                   |

| 3   | SAE1-SCHREIBVERSUCH | Schreibvorgang gestartet     |

| 4   | SAE1-RFULL          | Empfangs-RAM SAE1 voll       |

| 5   | SAE1-WR             | SAE1 Schreiben               |

| 6   | SAE1-SEBER          | Schnittstelle sendebereit    |

| 7   | SAE1-EMBER          | Schnittstelle empfangsbereit |

Tabelle 12 Statuswort ZZK-RD/2

| Bit | Betriebszustand     | Funktion                     |

|-----|---------------------|------------------------------|

| 0   | SAE2-LESEVERSUCH    | Lesevorgang gestartet        |

| 1   | SAE2-TEMPTY         | Sende-RAM SAE2 leer          |

| 2   | SAE2-RD             | SAE2 Lesen                   |

| 3   | SAE2-SCHREIBVERSUCH | Schreibvorgang gestartet     |

| 4   | SAE2-RFULL          | Empfangs-RAM SAE2 voll       |

| 5   | SAE2-WR             | SAE2 Schreiben               |

| 6   | SAE2-SEBER          | Schnittstelle sendebereit    |

| 7   | SAE2-EMBER          | Schnittstelle empfangsbereit |

In der folgenden Beschreibung werden die Statusworte der Ports FAH und F8H ausführlich erläutert.

Alle Statussignale sind LOW aktiv. Das Symbol "Sx" steht für SAE1 oder SAE2, die Funktionsgruppen Pufferspeicher und Kontrolllogik sind immer bezogen auf die entsprechende Hälfte der Schnittstelle ZZK.

Tabelle 13 Statuswort der Input-Ports FAH und F8H

| Bit | Signalname         | Wert | Funktion                                                                                                                                                                                                                                                                                           |

|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Sx-LESE-VERSUCH    | 0    | Die SAE hat das Lesen von Daten aus der Schnittstelle ZZK gestartet. Der Zustand wird rückgesetzt, wenn der DKo neue Daten in den Puffer eingeschrieben hat.                                                                                                                                       |

|     |                    | 1    | Initialwert                                                                                                                                                                                                                                                                                        |

| 1   | Sx-TEMPTY          | 0    | Initialwert<br>Der Sendepuffer ist logisch leer, d.h. die SAE hat den Datenblock vollständig gelesen.                                                                                                                                                                                              |

|     |                    | 1    | Der Sendepuffer ist nur teilweise oder gar nicht gelesen worden.                                                                                                                                                                                                                                   |

| 2   | Sx-RD              | 0    | Initialwert<br>Die SAE hat einen Lesezyklus eröffnet, um einen Datenblock aus dem Sendepuffer zu lesen. Die Schnittstelle ZZK hat die Betriebsweise SAE-LESEN eingestellt. Einen Zugriff des DKo-Prozessors auf den Sende- und Empfangspuffer der aktiven Hälfte ist in dieser Zeit nicht möglich. |

|     |                    | 1    | Die SAE greift nicht auf den Sendepuffer zu (sie hat keinen Lesezyklus eröffnet).                                                                                                                                                                                                                  |

| 3   | Sx-SCHREIB-VERSUCH | 0    | Die SAE hat das Schreiben von Daten in die Schnittstelle ZZK begonnen. Der Zustand wird durch die SW rückgesetzt, wenn nach Beenden des Schreibens (Sx-RFULL) die Daten in den DKo übertragen worden sind.                                                                                         |

|     |                    | 1    | Initialwert<br>Der Empfangspuffer ist leer und die SAE hat noch keinen Schreibzyklus für den nächsten Datenblock begonnen.                                                                                                                                                                         |

| 4   | Sx-RFULL           | 0    | Die SAE hat einen Datenblock vollständig in den Empfangspuffer geschrieben.                                                                                                                                                                                                                        |

|     |                    | 1    | Initialwert<br>Der Empfangspuffer ist logisch leer, d.h. der DKo-Prozessor hat den eingeschriebenen Datenblock im Empfangspuffer gelesen, und es wurde noch kein neuer Datenblock vollständig übertragen.                                                                                          |

Fortsetzung Tabelle 13

| Bit | Signalname | Wert | Funktion                                                                                                                                                                                                                                      |

|-----|------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | Sx-WR      | 0    | Die SAE hat einen Schreibzyklus eröffnet, um einen Datenblock in den Empfangspuffer zu übertragen. Die Betriebsweise SAE-Schreiben wurde eingestellt. Ein Zugriff des DKo-Prozessors auf dieser Hälfte ist während dieser Zeit nicht möglich. |

|     |            | 1    | Initialwert<br>Die SAE greift nicht auf den Empfangspuffer zu (sie hat keinen Schreibzyklus eröffnet).                                                                                                                                        |

| 6   | Sx-SEBER   | 0    | Initialwert<br>Die SAE darf einen Lesezyklus eröffnen, um einen Datenblock des Sendepuffers zu lesen, d.h. die Schnittstelle ZZK ist sendebereit (Datenrichtung vom DKo zur SAE)                                                              |

|     |            | 1    | Die SAE darf keinen Lesezyklus eröffnen, um einen Datenblock des Sendepuffers zu lesen.                                                                                                                                                       |

| 7   | Sx-EMBER   | 0    | Die SAE darf einen Schreibzyklus eröffnen, um einen Datenblock in den Empfangspuffer zu schreiben, d.h. die Schnittstelle ZZK ist empfangsbereit (Datenrichtung von SAE zum DKo).                                                             |

|     |            | 1    | Initialwert<br>Die SAE darf keinen Schreibzyklus eröffnen um einen Datenblock in den Empfangspuffer zu schreiben.                                                                                                                             |

Die Software kann über die Output-Ports F0H bis F4H und E8H bis ECH die Kontrollogik der Schnittstelle ZZK bedienen.

Nachfolgend werden die über die Output-Ports (OUTPUT S1, OUTPUT S2) gesendeten Kommandos an die Kontrollogik ausführlich beschrieben. Die Freigabe der Ports wird mit DKO-WR-L vorgenommen.

Tabelle 14 Kommandos der Output-Ports S1, S2

| Port     | Signalname    | Funktion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

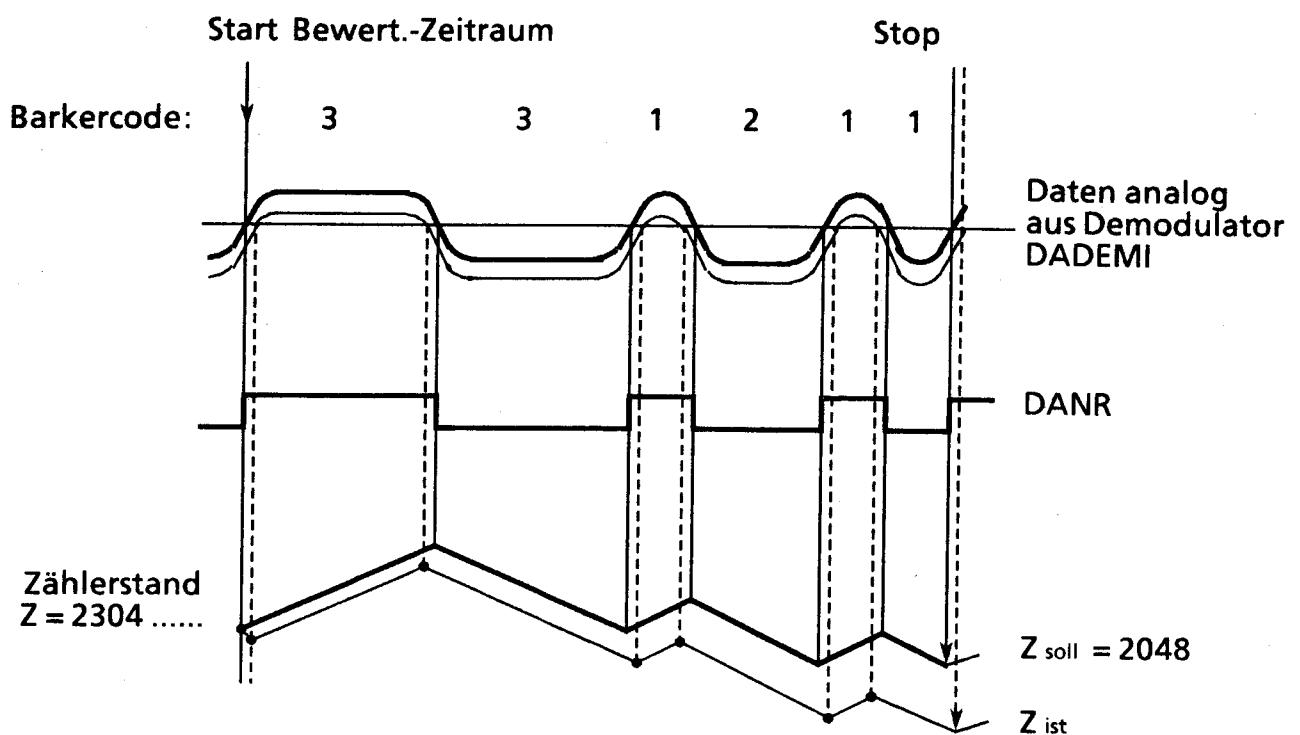

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|